# **SL8X305 Microcontroller**

Legacy Device: Philips/Signetics S8X305

#### **FEATURES**

- Fetch, Decode, and Execute a 16-bit Instruction in a minimum of 200ns (one machine cycle)

- Bit-oriented instruction set (addressable single- or multiple-bit subfields)

- Separate buses for instruction, instruction Address and 3– State I/O

- Thirteen 8-bit general-purpose working registers

- Source/destination architecture

- Bipolar low-power Schottky technology/TTL inputs and outputs

- On-chip oscillator and timing generation

- Single +5V supply

- Multiple package options

#### PRODUCT DESCRIPTION

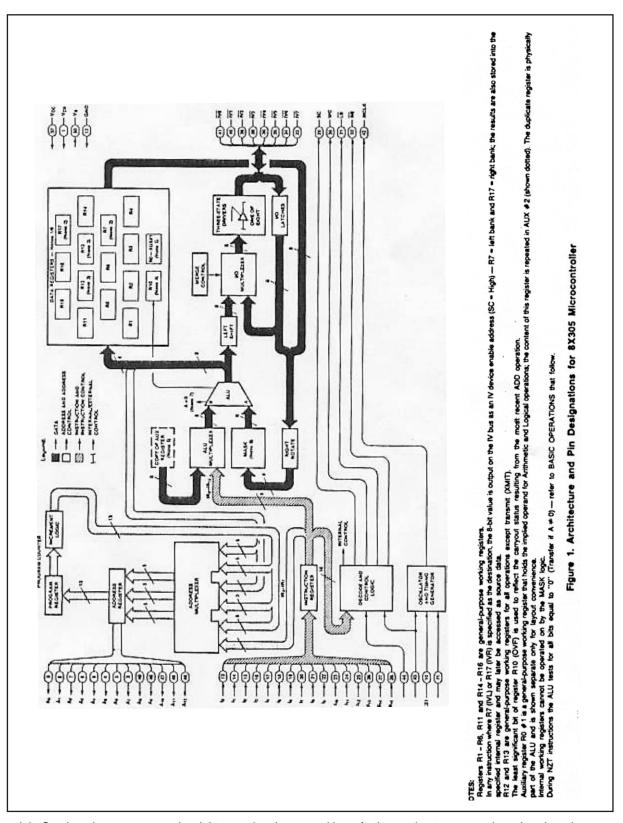

The Signetics 8X305 Microcontroller (Figure 1) is a high–speed bipolar microprocessor implemented with low–power Schottky technology. In a single chip, the 8X305 combines speed, flexibility, and a bit–oriented instruction set. These features and other basic characteristics of the chip combine to provide cost–effective solutions for a broad range of applications. The 8X305 is particularly useful in systems that require high–speed bit manipulations — sophisticated controllers, data communications, very fast interface control, and other applications of a similar nature.

The 8X305 can fetch, decode, and execute a 16-bit instruction word in a minimum of 200ns. Within one instruction cycle, the 8-bit data-processing path can be programmed to rotate, mask, shift, and/or merge single or multiple bit subfields and, in addition, perform an ALU operation; in the same instruction, an external data field can be input, processed, and output to a specified destination — likewise, single or multiple bit data fields can be internally moved from a given source to a given destination. To summarize, fixed or variable-length data fields can be fetched, processed, operated on by the ALU, and moved to a different location — all in a timeframe of 200ns. To interface with I/O and program memory, the 8X305 uses a 13-bit instruction bus, an 8-bit bidirectional multiplexed I/O data/address bus and a 5-bit I/O control bus.

A wide selection of I/O devices, interface chips, and special-purpose parts are available for systems use. In most applications, the more powerful 8X305 is functionally interchangeable with its predecessor — the 8X300.

## ABSOLUTE MAXIMUM RATINGS

| PARAMETER        | DESCRIPTION                     | RATING      | UNIT |  |

|------------------|---------------------------------|-------------|------|--|

| V <sub>CC</sub>  | Supply voltage                  | +7.0        | ٧    |  |

| X1, X2           | Crystal input voltage           | 2.0         | ٧    |  |

| All other pins   | Logic input pins V <sub>I</sub> | 5.5         | , V  |  |

| T <sub>STG</sub> | Storage temperature range       | -65 to +150 | °C   |  |

# DC ELECTRICAL CHARACTERISTICS 4.5V $\leq$ V<sub>CC</sub> $\leq$ 5.5V, -55°C $\leq$ T<sub>C</sub> $\leq$ +125°C unless otherwise noted.

| SYMBOL          |                              |                                                                                                    | LIMITS     |                   |                            |          | 0011111111                                                               |  |

|-----------------|------------------------------|----------------------------------------------------------------------------------------------------|------------|-------------------|----------------------------|----------|--------------------------------------------------------------------------|--|

|                 | PARAMETER                    | TEST CONDITIONS                                                                                    | Min        | Тур               | Max                        | UNIT     | COMMENTS                                                                 |  |

| V <sub>CC</sub> | Supply voltage               |                                                                                                    | 4.75       | 5.0               | 5.5                        | ٧        |                                                                          |  |

| VIH             | High level input voltage     |                                                                                                    | 0.6<br>2.0 |                   | 2.0                        | ٧        | X1 and X2<br>All other pins                                              |  |

| VIL             | Low level input voltage      |                                                                                                    |            |                   | 0.4<br>0.8                 | ٧        | X1 and X2<br>All other pins                                              |  |

| V <sub>OH</sub> | High level output voltage    | V <sub>CC</sub> = MIN; I <sub>OH</sub> = -3mA                                                      | 2.4        |                   |                            | ٧        |                                                                          |  |

| V <sub>OL</sub> | Low level output voltage     | V <sub>CC</sub> = MIN; I <sub>OL</sub> = 6mA<br>V <sub>CC</sub> = MIN; I <sub>OL</sub> = 16mA      | <          |                   | 0.55<br>0.55               | ٧        | A <sub>0</sub> through A <sub>12</sub><br>All other outputs              |  |

| V <sub>CR</sub> | Regulator voltage            | V <sub>CC</sub> = 5V                                                                               |            | 3.5<br>3.1<br>2.6 |                            | ٧        | T <sub>A</sub> = -55°C<br>T <sub>A</sub> = 0°C<br>T <sub>C</sub> = 125°C |  |

| V <sub>IK</sub> | Input clamp voltage          | V <sub>CC</sub> = MIN; I <sub>I</sub> = -10mA                                                      |            |                   | -1.5                       | ٧        | Crystal inputs X1 and X2 do not have internal clamp diodes.              |  |

| l <sub>IH</sub> | High level input current     | V <sub>CC</sub> = MAX V <sub>IH</sub> = 0.6V<br>V <sub>IH</sub> = 4.5V                             |            |                   | 4.0<br>50                  | mA<br>μA | X1 and X2<br>All other pins                                              |  |

| IIL             | Low-level input current      | V <sub>CC</sub> = MAX; V <sub>IL</sub> = 0.4V                                                      |            |                   | -3<br>-0.3<br>-1.6<br>-0.4 | mA       | X1 and X2<br>IV0 - IV7<br>I0 - I15<br>HALT and RESET                     |  |

| los             | Short circuit output current | V <sub>CC</sub> = MAX; (Note: At any time, no more than one output should be connected to ground.) | -30        |                   | -140                       | mA       | All output pins                                                          |  |

| Icc             | Supply current               | V <sub>CC</sub> = MAX                                                                              |            |                   | 175<br>205                 | mA.      | T <sub>C</sub> = 125°C<br>T <sub>A</sub> = -55°C                         |  |

| IREG            | Regulator control            | V <sub>CC</sub> = 5.0V                                                                             | -10        |                   | -25                        | mA       | Max available base drive for series-pass transistor                      |  |

| ICR             | Regulator current            | V <sub>CC</sub> = MAX                                                                              |            |                   | 180<br>260                 | mA       | T <sub>C</sub> = 125°C<br>T <sub>A</sub> = -55°C                         |  |

#### NOTES:

<sup>1.</sup> Operating temperature ranges are guaranteed after thermal equilibrium has been reached.

<sup>2.</sup> All voltages measured with respect to ground terminal.

# AC ELECTRICAL CHARACTERISTICS CONDITIONS: 4.5V < V $_{CC}$ < 5.5V; -55°C < T $_{C}$ < 125°C LOADING: (See test circuits)

| SYMBOL            | PARAMETER (NOTE 1)                                                                                            | LIMITS (INSTRUCTION<br>CYCLE TIME = 200ns) |     |        | LIMITS (INSTRUCTION<br>CYCLE TIME > 200ns) |     |                                           | UN- | COMMENTS       |

|-------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----|--------|--------------------------------------------|-----|-------------------------------------------|-----|----------------|

|                   |                                                                                                               | Min                                        | Тур | Max    | Min                                        | Тур | Max                                       | ITS |                |

| T <sub>PC</sub>   | Processor cycle time                                                                                          | 200                                        |     |        | 200                                        |     |                                           | ns  |                |

| T <sub>CP</sub>   | X1 clock period                                                                                               | 100                                        |     |        | 100                                        |     |                                           | ns  | 34             |

| ТСН               | X1 clock high time                                                                                            | 50                                         |     |        | 50                                         |     |                                           | ns  |                |

| T <sub>CL</sub>   | X1 clock low time                                                                                             | 50                                         |     |        | 50                                         |     |                                           | ns  |                |

| T <sub>MCL</sub>  | MCLK low delay                                                                                                | 15                                         |     | 40     | 15                                         |     | 40                                        | ns  |                |

| T <sub>W</sub>    | MCLK pulse width                                                                                              | 30                                         |     | 60     | T <sub>4Q</sub> - 10                       |     | T <sub>4Q</sub> + 10                      | ns  | Note 2         |

| T <sub>MODO</sub> | Output driver turn on time MCLK falling edge                                                                  | 125                                        |     | 148    | T <sub>1Q</sub> +<br>T <sub>2Q</sub> + 25  |     | T <sub>1Q</sub> + T <sub>2Q</sub> + 45    | ns  | Note 9         |

| T <sub>DI</sub>   | Output driver turn-on time (SC/WC rising edge)                                                                | 20                                         |     |        | 20                                         |     |                                           | ns  | Note 10        |

| T <sub>DD</sub>   | Input data to output data                                                                                     | 75                                         |     | 105    | 75                                         |     | 105                                       | ns  |                |

| T <sub>MHS</sub>  | MCLK falling edge to HALT falling edge                                                                        |                                            |     | 30     |                                            |     | T <sub>1Q</sub> - 20                      | ns  | Note 2         |

| T <sub>MHH</sub>  | HALT hold time<br>(MCLK falling edge)                                                                         | 65                                         |     |        | T <sub>1Q</sub> + 15                       |     |                                           | ns  | Note 2         |

| TACC              | Program storage access time                                                                                   |                                            |     | 60     |                                            |     |                                           | ns  | Note 12        |

| T <sub>IO</sub>   | I/O port output enable time (LR/RB to valide IV data input)                                                   |                                            |     | 20     |                                            |     |                                           | ns  |                |

| T <sub>MAS</sub>  | MCLK falling edge to address stable                                                                           |                                            |     | 140    |                                            |     | T <sub>1Q</sub> +<br>T <sub>2Q</sub> + 40 | ns  | Notes 2, 3, &  |

| TIA               | Instruction to address                                                                                        |                                            |     | 140    |                                            |     | T <sub>2Q</sub> + 90                      | ns  | Notes 2, 3 & 5 |

| TIVA              | Input data to address                                                                                         |                                            |     | 95     |                                            |     | 85                                        | ns  | Notes 3 & 6    |

| T <sub>MIS</sub>  | MCLK falling edge to instruction stable                                                                       |                                            |     | 25     |                                            |     | T <sub>1Q</sub> - 20                      | ns  | Notes 2 & 10   |

| T <sub>MIH</sub>  | Instruction hold time (MCLK falling edge) 55                                                                  |                                            |     |        | T <sub>1Q</sub> + 5                        |     |                                           | ns  | Notes 2 & 8    |

| T <sub>MWH</sub>  | MCLK falling edge to SC/WC rising edge                                                                        | 100                                        |     | 128    | T <sub>1Q</sub> +<br>T <sub>2Q</sub> + 5   |     | T <sub>1Q</sub> + T <sub>2Q</sub> + 25    | ns  | Notes 2 & 11   |

| T <sub>MWL</sub>  | MCLK falling edge to SC/WC falling edge                                                                       | 0                                          |     | 15     | 0                                          |     | 15                                        | ns  |                |

| T <sub>MIBS</sub> | MCLK falling edge to LB/RB (Input phase)                                                                      | 8                                          |     | 25     | 8                                          |     | 25                                        | ns  |                |

| T <sub>IIBS</sub> | Instruction to LB/RB (Input phase)                                                                            |                                            |     | 25     |                                            |     | 25                                        | ns  |                |

| T <sub>MOBS</sub> | MCLK falling edge to LB/RB 115 145 T <sub>1Q</sub> + T <sub>1Q</sub> + T <sub>1Q</sub> + T <sub>2Q</sub> + 45 |                                            | ns  | Note 2 |                                            |     |                                           |     |                |

| T <sub>MIDS</sub> | MCLK falling edge to input data stable                                                                        |                                            |     | 55     |                                            |     | T <sub>1Q</sub> +<br>T <sub>2Q</sub> - 45 | ns  | Note 2         |

| T <sub>MIDH</sub> | Input data hold time<br>(MCLK falling edge)                                                                   | 115                                        |     |        | T <sub>1Q</sub> + T <sub>2Q</sub> + 15     |     |                                           | ns  | Notes 2 & 11   |

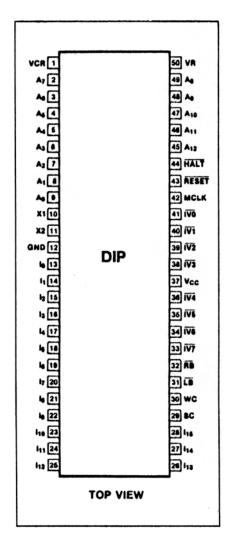

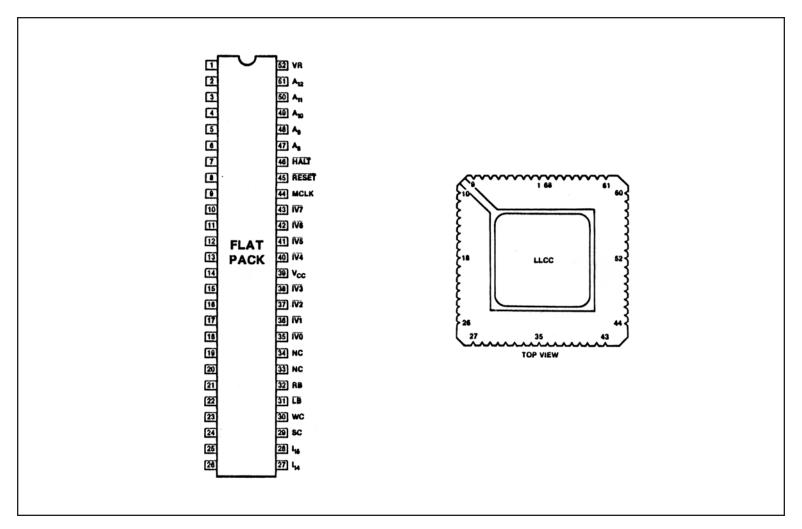

# PIN CONFIGURATIONS (Continued)

#### PIN DESCRIPTION

| FLATPACK   | LLCC            | DIP        | IDENTIFIED                       | EUNOTION                                                                                                                                             |

|------------|-----------------|------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN NO.    | PIN NO.         | PIN NO.    | IDENTIFIER                       | FUNCTION                                                                                                                                             |

| 1          | 1, 68           | 1          | VCR                              | Regulated voltage input from series-pass transistor (2N5320 or equivalent).                                                                          |

| 2-9, 47-51 | 4-11, 62-66     | 2-9, 45-49 | A <sub>0</sub> - A <sub>12</sub> | Program Address Lines: These active-high outputs permit direct addressing of up to 8192 words of program storage; $A_{12}$ is least significant bit. |

| 10-11      | 12, 13          | 10, 11     | X1, X2                           | Timing generator connections for a capacitor, a series resonant crystal, or an external clock source with complementary outputs.                     |

| 12         | 2,3, 14-16      | 12         | GND                              | Ground.                                                                                                                                              |

| 13-28      | 17-23,<br>28-36 | 13-28      | 10-115                           | Instruction Lines: These active-high input lines receive 16-bit instructions from program storage; I <sub>15</sub> is least significant bit.         |

| 29         | 37              | 29         | sc                               | Select Command: When high (binary 1), an address is being output on pins $\overline{\text{IVO}}$ through $\overline{\text{IV7}}$ .                   |

| 31         | 38              | 30         | wc                               | Write Command: When high (binary 1), data is being output on pins VO through V7.                                                                     |

## PIN DESCRIPTION (Continued)

| FLATPACK                |                            |                 | IDENTIFIER      | FUNCTION                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|-------------------------|----------------------------|-----------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIN NO. PIN NO. PIN NO. |                            |                 |                 |                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 31                      | 39                         | 31              | LB              | <b>Left Bank Control:</b> When low (binary 0), devices connected to the Left Bank are accessed. (Note. Typically, the $\overline{LB}$ signal is tied to the $\overline{ME}$ input pin of I/O peripherals).                                                                                                                                                       |  |  |  |

| 32                      | 45                         | 32              | RB              | Right Bank Control: When low (binary 0), devices connected to the Right Bank are accessed (Note. Typically, the RB signal is tied to the RE input pin of I/O peripherals).                                                                                                                                                                                       |  |  |  |

| 35-38,<br>40-43         | 46-49,<br>55-58            | 33-36,<br>38-41 | IV0 – IV7       | Interface Vector (Input/Output Bus) — these bidirectional active-low three-state lines communicate data and/or addresses to I/O devices and memory locations. A low voltage level equals a binary "1"; V7 is Least Significant Bit.                                                                                                                              |  |  |  |

| 39                      | 50-52                      | 37              | V <sub>CC</sub> | +5V power supply.                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 44                      | 59                         | 42              | MCLK            | Master Clock: This active-high output signal is used for clocking I/O devices and/<br>or synchronization of external logic.                                                                                                                                                                                                                                      |  |  |  |

| 45                      | 60                         | 43              | RESET           | When RESET input is low (binary 0), the 8X305 is initialized — sets Program Counter/Address Register to zero and inhibits MCLK. For the period of time RESET is low, the Left Bank/Right Bank (LB/RB) signals are forced high asynchronously.                                                                                                                    |  |  |  |

| 46                      | 61                         | 44              | HALT            | When HALT input is low (binary 0), internal operation of the 8X305 stops at the start of next instruction; MCLK is not inhibited nor is any internal register affected; however, both the Left Bank/Right Bank (LB/RB) signals are synchronously driven high during the first quarter of the instruction cycle time and remain high during the time HALT is low. |  |  |  |

| 52                      | 67                         | 50              | VR              | Internally-generated reference output voltage for external series-pass regulator transistor.                                                                                                                                                                                                                                                                     |  |  |  |

| 33, 34                  | 24-27,<br>40-44,<br>53, 54 | -               | No<br>Connect   |                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

Lansdale Semiconductor reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Lansdale does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. "Typical" parameters which may be provided in Lansdale data sheets and/or specifications can vary in different applications, and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by the customer's technical experts. Lansdale Semiconductor is a registered trademark of Lansdale Semiconductor, Inc.