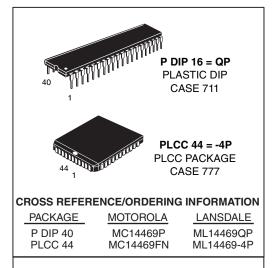

# ML14469 Addressable Asynchronous Receiver/Transmitter CMOS

Legacy Device: Motorola MC14469

The ML14469 receives one or two 11-bit words in a serial data stream. One of the incoming words contains the address and when the address matches, the ML14469 then transmits information in two 11-bit word data streams. Each of the transmitted words contains eight data bits, an even parity bit, and start and stop bits.

The received word contains seven address bits with the address of the ML14469 set on seven pins. Therefore, 2<sup>7</sup> or 128 units can be interconnected in simplex or full–duplex data transmission. In addition to the address received, seven command bits may be received for general–purpose data or control use.

The ML14469 finds application in transmitting data from remote analog—to—digital converters, remote MPUs, or remote digital transducers to the master computer or MPU.

- Supply Voltage Range: 4.5 V to 18 V

- Low Quiescent Current: 75 μA Maximum @ 5 V, 25°C

- Guaranteed Data Rates to 4800 Baud @ 5 V, to 9600 Baud @ 12 V

- Receive Serial to Parallel Transmit — Parallel to Parallel

- Transmit and Receive Simultaneously in Full Duplex

- Crystal or Resonator Operation for On-Chip Oscillator

- See Application Note AN806A

- Chip Complexity: 1200 FETs or 300 Equivalent Gates

- Operating Temperature Range  $T_A = -40^{\circ}$  to  $+85^{\circ}$ C

**Note**: Lansdale lead free (**Pb**) product, as it becomes available, will be identified by a part number prefix change from **ML** to **MLE**.

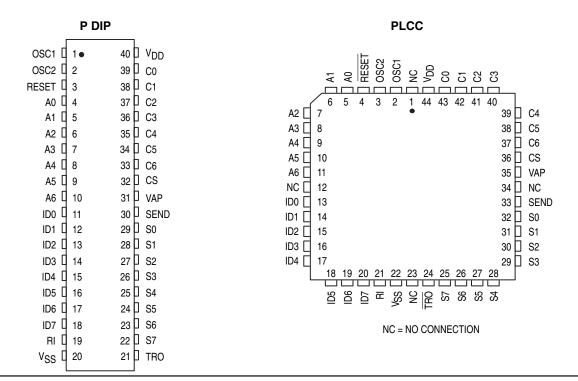

#### **PIN ASSIGNMENTS**

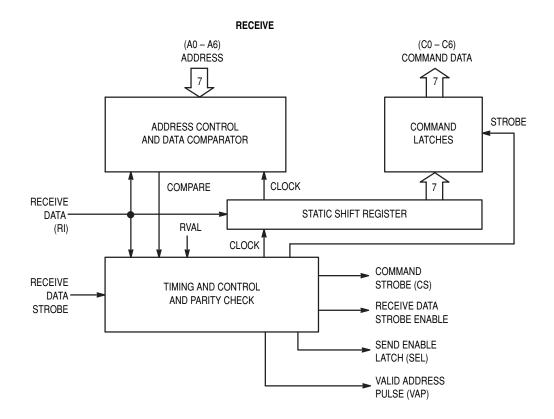

# **BLOCK DIAGRAM**

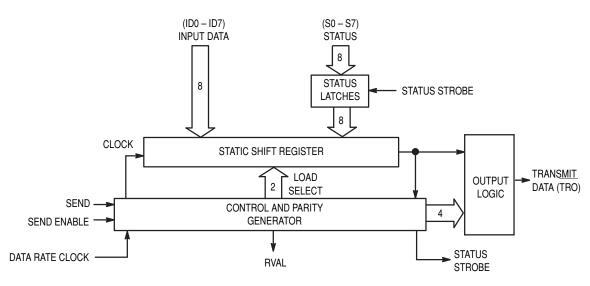

### **TRANSMIT**

# $\textbf{MAXIMUM RATINGS} \ (\text{Voltages referenced to V}_{SS})$

| Rating                      | Symbol           | Value                          | Unit |

|-----------------------------|------------------|--------------------------------|------|

| DC Supply Voltage           | V <sub>DD</sub>  | - 0.5 to + 18                  | V    |

| Input Voltage, All Inputs   | V <sub>in</sub>  | – 0.5 to V <sub>DD</sub> + 0.5 | V    |

| DC Current Drain per Pin    | 1                | 10                             | mA   |

| Operating Temperature Range | TA               | - 40 to + 85                   | С    |

| Storage Temperature Range   | T <sub>stg</sub> | - 65 to + 150                  | С    |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high–impedance circuit. For proper operation it is recommended that  $V_{in}$  and  $V_{out}$  be constrained to the range  $V_{SS} \leq (V_{in} \mbox{ or } V_{out}) \leq V_{DD}.$

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either V<sub>SS</sub> or V<sub>DD</sub>).

# **ELECTRICAL CHARACTERISTICS** (Voltages referenced to V<sub>SS</sub>)

|                                                                                                                           |           |                 |                        | - 40 C                               |                      | 25 C                                  |                      | 85 C                                |                      |      |

|---------------------------------------------------------------------------------------------------------------------------|-----------|-----------------|------------------------|--------------------------------------|----------------------|---------------------------------------|----------------------|-------------------------------------|----------------------|------|

| Characteristic                                                                                                            |           | Symbol          | V <sub>DD</sub>        | Min                                  | Max                  | Min                                   | Max                  | Min                                 | Max                  | Unit |

| Output Voltage<br>V <sub>in</sub> = V <sub>DD</sub> or 0                                                                  | "0" Level | V <sub>OL</sub> | 5.0<br>10<br>15        |                                      | 0.05<br>0.05<br>0.05 | _<br>_<br>_                           | 0.05<br>0.05<br>0.05 |                                     | 0.05<br>0.05<br>0.05 | V    |

| $V_{in} = 0$ or $V_{DD}$                                                                                                  | "1" Level | VOH             | 5.0<br>10<br>15        | 4.95<br>9.95<br>14.95                | _<br>_<br>_          | 4.95<br>9.95<br>14.95                 | _<br>_<br>_          | 4.95<br>9.95<br>14.95               | _<br>_<br>_          | V    |

| Input Voltage (Except OSC1)  V <sub>O</sub> = 4.5 or 0.5 V  V <sub>O</sub> = 9.0 or 1.0 V  V <sub>O</sub> = 13.5 or 1.5 V | "0" Level | V <sub>IL</sub> | 5.0<br>10<br>15        | _<br>_<br>_                          | 1.5<br>3.0<br>4.0    | _<br>_<br>_                           | 1.5<br>3.0<br>4.0    | _<br>_<br>_                         | 1.5<br>3.0<br>4.0    | V    |

| V <sub>O</sub> = 0.5 or 4.5 V<br>V <sub>O</sub> = 1.0 or 9.0 V<br>V <sub>O</sub> = 1.5 or 13.5 V                          | "1" Level | VIH             | 5.0<br>10<br>15        | 3.5<br>7.0<br>11                     | _<br>_<br>_          | 3.5<br>7.0<br>11                      | _<br>_<br>_          | 3.5<br>7.0<br>11                    | _<br>_<br>_          | ٧    |

| Output Drive Current (Except OSC2)  VOH = 2.5 V  VOH = 4.6 V  VOH = 9.5 V  VOH = 13.5 V                                   | Source    | ЮН              | 5.0<br>5.0<br>10<br>15 | - 1.0<br>- 0.2<br>- 0.5<br>- 1.4     | _<br>_<br>_<br>_     | - 0.8<br>- 0.16<br>- 0.4<br>- 1.2     | _<br>_<br>_<br>_     | - 0.6<br>- 0.12<br>- 0.3<br>- 1.0   | _<br>_<br>_<br>_     | mA   |

| V <sub>OL</sub> = 0.4 V<br>V <sub>OL</sub> = 0.5 V<br>V <sub>OL</sub> = 1.5 V                                             | Sink      | lOL             | 5.0<br>10<br>15        | 0.52<br>1.3<br>3.6                   | _<br>_<br>_          | 0.44<br>1.1<br>3.0                    | _<br>_<br>_          | 0.36<br>0.9<br>2.4                  | _<br>_<br>_          | mA   |

| Output Drive Current (OSC2 Only)  VOH = 2.5 V  VOH = 4.6 V  VOH = 9.5 V  VOH = 13.5 V                                     | Source    | ЮН              | 5.0<br>5.0<br>10<br>15 | - 0.19<br>- 0.04<br>- 0.09<br>- 0.29 | _<br>_<br>_<br>_     | - 0.16<br>- 0.035<br>- 0.08<br>- 0.27 | _<br>_<br>_<br>_     | - 0.13<br>- 0.03<br>- 0.06<br>- 0.2 | _<br>_<br>_<br>_     | mA   |

| V <sub>OL</sub> = 0.4 V<br>V <sub>OL</sub> = 0.5 V<br>V <sub>OL</sub> = 1.5 V                                             | Sink      | lOL             | 5.0<br>10<br>15        | 0.1<br>0.17<br>0.5                   | _<br>_<br>_          | 0.085<br>0.14<br>0.42                 | _<br>_<br>_          | 0.07<br>0.1<br>0.3                  | _<br>_<br>_          | mA   |

| OSC Frequency*                                                                                                            |           | fosc            | 4.5<br>12              | 0<br>0                               | 400<br>800           | 0<br>0                                | 365<br>730           | 0<br>0                              | 310<br>620           | kHz  |

| Input Current                                                                                                             |           | l <sub>in</sub> | 15                     | _                                    | ± 0.3                | _                                     | ± 0.3                | _                                   | ± 1.0                | А    |

| Pull-Up Current (A0 - A6, ID0 - ID7)                                                                                      |           | l <sub>UP</sub> | 15                     | 12                                   | 120                  | 10                                    | 100                  | 8.0                                 | 85                   | Α    |

| Input Capacitance (V <sub>in</sub> = 0)                                                                                   |           | C <sub>in</sub> |                        | _                                    | _                    | _                                     | 7.5                  | _                                   |                      | pF   |

| Quiescent Current (Per Package)                                                                                           |           | lDD             | 5.0<br>10<br>15        | _<br>_                               | 75<br>150<br>300     | _<br>_                                | 75<br>150<br>300     | _<br>_                              | 565<br>1125<br>2250  | Α    |

| Supply Voltage                                                                                                            |           | V <sub>DD</sub> | _                      | + 4.5                                | + 18                 | + 4.5                                 | + 18                 | + 4.5                               | + 18                 | ٧    |

<sup>\* 310</sup> kHz at 85 C guarantees 4800 baud; 620 kHz at 85 C guarantees 9600 baud.

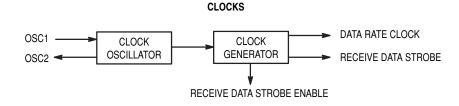

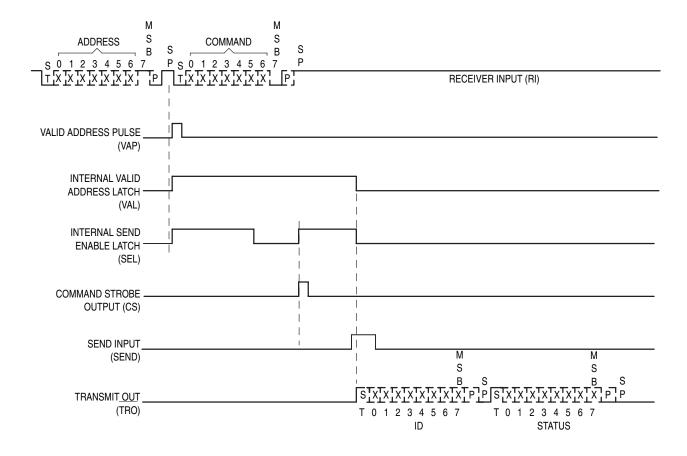

Figure 1. Data Format and Corresponding Data Position and Pins for MC14469 and MC6850

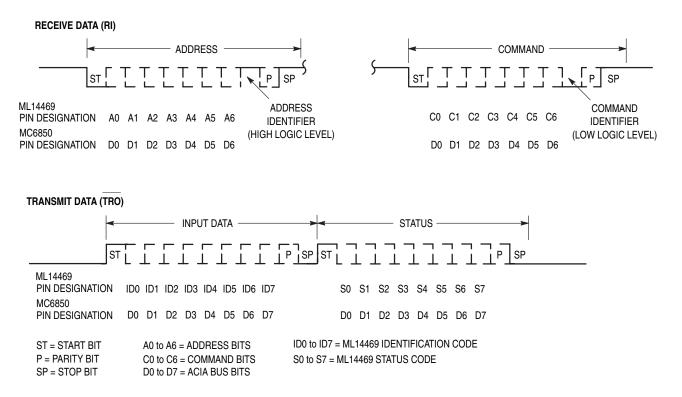

Figure 2. Typical Receive/Send Cycle

#### PIN DESCRIPTIONS

# A0 – A6 Address Inputs

These inputs are the address setting pins which contain the address match for the received signal. Pins A0 – A6 have on–chip pull–up resistors.

# C0 - C6

#### **Command Word**

These pins are the readout of the general–purpose command word which is the second word of the received signal.

#### CS

#### **Command Strobe**

This is the output for the command strobe signifying a valid set of command data (C0 – C6). The pulse width is one oscillator cycle. For example, when a 307.2 kHz ceramic resonator is used, the pulse width is approximately 3  $\mu$ s.

# ID0 – ID7 Input Data Pins

These pins contain the input data for the first eight bits of data to be transmitted. Pins ID0 – ID7 have on—chip pull—up resistors.

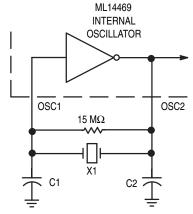

#### OSC1, OSC2

# **Oscillator Input and Oscillator Output**

These pins are the oscillator input and output (see Figure 3).

# **RESET**

# Reset

When this pin is pulled low for a minimum of 700 ns, the circuit is reset and ready for operation.

#### RI

# **Receive Input**

This is the receive input pin.

#### S0 - S7

# **Second or Status Input Data**

These pins contain the input data for the second eight bits of data to be transmitted.

# **SEND**

#### Send

This pin accepts the send command after receipt of an address.

# TRO

# **Transmit Register Output Signal**

This pin transmits the outgoing signal. Note that it is inverted from the incoming signal. It must go through one stage of

inversion if it is to drive another ML14469.

#### VAP

#### Valid Address Pulse

This is the output for the valid address pulse upon receipt of a matched incoming address.

# VDD Positive Power Supply

This pin is the package positive power supply connection. This pin may range from +4.5 V to +18 V with respect to VSS.

# VSS

# **Negative Power Supply**

This pin is the negative power supply connection. Normally this pin is system ground.

#### **OPERATING CHARACTERISTICS**

The receipt of a start bit on the receive input (RI) line causes the receive clock to start at a frequency equal to that of the oscillator divided by 64. All received data is strobed in at the center of a receive clock period. The start bit is followed by eight data bits. Seven of the bits are compared against states of the address of the particular circuit (A0 –A6). Address is latched 31 clock cycles after the end of the start bit of the incoming address. The eighth bit signifies an address word "1" or a command word "0". Next, a parity bit is received and checked by the internal logic for even parity. Finally a stop bit is received. At the completion of the cycle if the address matches, a valid address pulse (VAP) occurs. Immediately following the address word, a command word is received. It also contains a start bit, eight data bits, even parity bit, and a stop bit. The eight data bits are composed of a seven-bit command, and a "0" which indicates a command word. At the end of the command word a command strobe pulse (CS) occurs.

A positive transition on the send input initiates the transmit sequence. Send must occur within seven bit times of CS. Again the transmitted data is made up of two eleven—bit words, i.e., address and command words. The data portion of the first word is made up from input data inputs (ID0 –ID7), and the data for the second word from second input data (S0 – S7) inputs. The data on inputs ID0 – ID7 is latched one clock before the falling edge of the start bit. The data on inputs S0 – S7 is latched on the rising edge of the start bit. The transmitted signal is the inversion of the received signal, which allows the use of an inverting amplifier to drive the lines. TRO begins either 1/2 or 1–1/2 bit times after send, depending where send occurs.

The oscillator can be crystal controlled or ceramic resonator controlled for required accuracy. OSC1 can be driven from an external oscillator (see Figure 3).

NOTE: For externally generated clock, drive OSC1, float OSC2.

$X1 = Ceramic Resonator: 307.2 kHz \pm 1 kHz for 4800 baud rate.$ C1 and C2 are sized per the ceramic resonator supplier's recommendation.

Ceramic Resonator Suppliers:\*

Figure 3. Oscillator Circuit

in no way suggests that this is a complete listing of ceramic resonator suppliers.

1.0 F 1. Morgan Matroc, Inc., Bedford, OH, 216/232-8600 2. Radio Materials Co., Attica, IN, 317/762-2491 \* Lansdale cannot recommend one supplier over another and

$1.0~\text{k}\Omega$ DATA LINE **GROUND LINE** RI TRO ۷DD ML14469 VSS

Figure 4. Rectified Power from Data Lines Circuit

$V_{DATA}$

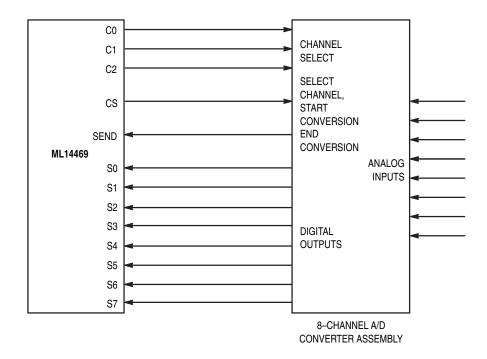

Figure 5. A-D Converter Interface

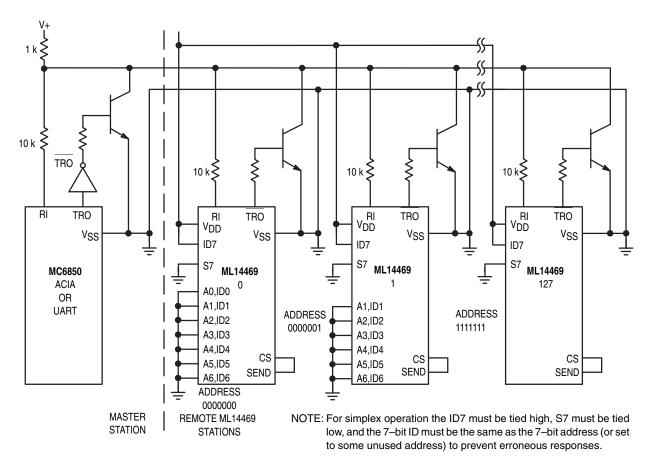

Figure 6. Single Line, Simplex Data Transmission

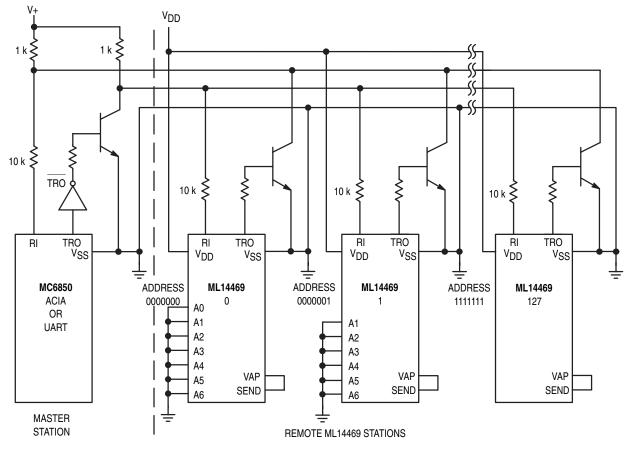

Figure 7. Double Line, Full Duplex Data Transmission

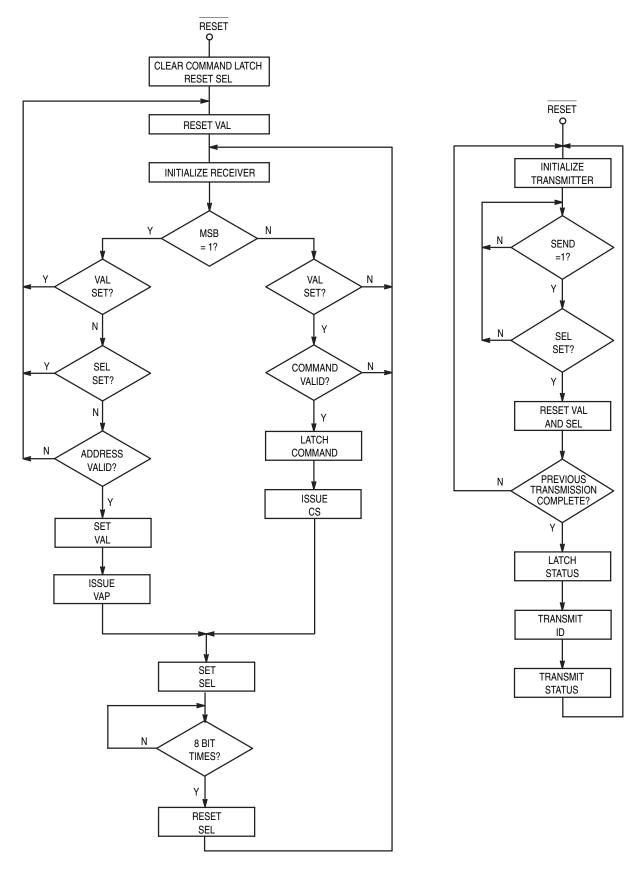

Figure 8. Flow Chart of ML14469 Operation

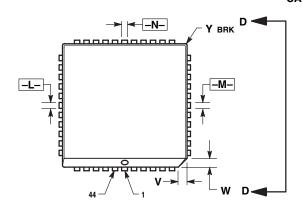

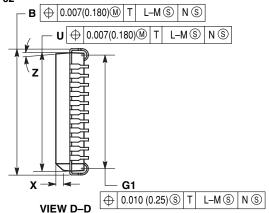

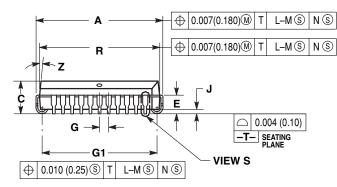

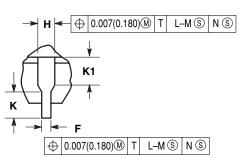

#### **OUTLINE DIMENSIONS**

PLCC 44 = -4P (ML14469-4P) PLCC PACKAGE **CASE 777-02**

# VIEW S

- OTES:

1. DATUMS -L., -M-, AND -N- ARE DETERMINED WHERE TOP OF LEAD SHOULDER EXITS PLASTIC BODY AT MOLD PARTING LINE.

2. DIMENSION G1, TRUE POSITION TO BE MEASURED AT DATUM -T-, SEATING PLANE.

3. DIMENSIONS R AND U DO NOT INCLUDE MOLD FLASH. ALLOWABLE MOLD FLASH IS 0.010 (0.25) PER SIDE.

- 4. DIMENSIONING AND TOLERANCING PER ANSI Y14 5M 1982

- 5. CONTROLLING DIMENSION: INCH.

- 5. CUNI HOLLING DIMENSION: INCH.

6. THE PACKAGE TOP MAY BE SMALLER THAN

THE PACKAGE BOTTOM BY UP TO 0.012

(0.300). DIMENSIONS R AND U ARE

DETERMINED AT THE OUTERMOST

EXTREMES OF THE PLASTIC BODY

EXCLUSIVE OF MOLD FLASH, TIE BAR BURRS,

GATE BURRS AND INTERI FAD FLASH BUT GATE BURRS AND INTERLEAD FLASH, BUT INCLUDING ANY MISMATCH BETWEEN THE TOP AND BOTTOM OF THE PLASTIC BODY.

7. DIMENSION H DOES NOT INCLUDE DAMBAR

- PROTRUSION OR INTRUSION. THE DAMBAR PROTRUSION(S) SHALL NOT CAUSE THE H DIMENSION TO BE GREATER THAN 0.037 (0.940). THE DAMBAR INTRUSION(S) SHALL NOT CAUSE THE H DIMENSION TO BE SMALLER THAN 0.025 (0.635).

|     | INCHES |           | MILLIMETERS |       |  |

|-----|--------|-----------|-------------|-------|--|

| DIM | MIN    | MAX       | MIN         | MAX   |  |

| Α   | 0.685  | 0.695     | 17.40       | 17.65 |  |

| В   | 0.685  | 0.695     | 17.40       | 17.65 |  |

| С   | 0.165  | 0.180     | 4.20        | 4.57  |  |

| Е   | 0.090  | 0.110     | 2.29        | 2.79  |  |

| F   | 0.013  | 0.019     | 0.33        | 0.48  |  |

| G   | 0.050  | 0.050 BSC |             | BSC   |  |

| Н   | 0.026  | 0.032     | 0.66        | 0.81  |  |

| J   | 0.020  | _         | 0.51        | _     |  |

| K   | 0.025  |           | 0.64        |       |  |

| R   | 0.650  | 0.656     | 16.51       | 16.66 |  |

| C   | 0.650  | 0.656     | 16.51       | 16.66 |  |

| ٧   | 0.042  | 0.048     | 1.07        | 1.21  |  |

| W   | 0.042  | 0.048     | 1.07        | 1.21  |  |

| Χ   | 0.042  | 0.056     | 1.07        | 1.42  |  |

| Υ   |        | 0.020     |             | 0.50  |  |

| Z   | 2°     | 10°       | 2°          | 10°   |  |

| G1  | 0.610  | 0.630     | 15.50       | 16.00 |  |

| K1  | 0.040  |           | 1.02        |       |  |

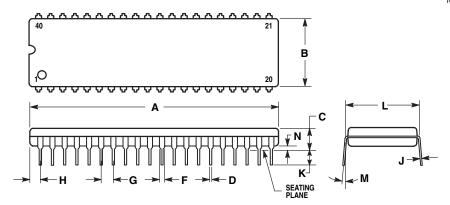

## **OUTLINE DIMENSIONS**

P DIP 40 = QP (ML14469QP) PLASTIC DIP CASE 711-03

#### NOTES:

- OTES:

1. POSITIONAL TOLERANCE OF LEADS (D), SHALL BE WITHIN 0.25 (0.010) AT MAXIMUM MATERIAL CONDITION, IN RELATION TO SEATING PLANE AND EACH OTHER.

- DIMENSION L TO CENTER OF LEADS WHEN FORMED PARALLEL.

- 3. DIMENSION B DOES NOT INCLUDE MOLD FLASH.

|     | MILLIN    | IETERS | INCHES    |       |  |

|-----|-----------|--------|-----------|-------|--|

| DIM | MIN       | MAX    | MIN       | MAX   |  |

| Α   | 51.69     | 52.45  | 2.035     | 2.065 |  |

| В   | 13.72     | 14.22  | 0.540     | 0.560 |  |

| С   | 3.94      | 5.08   | 0.155     | 0.200 |  |

| D   | 0.36      | 0.56   | 0.014     | 0.022 |  |

| F   | 1.02      | 1.52   | 0.040     | 0.060 |  |

| G   | 2.54 BSC  |        | 0.100 BSC |       |  |

| Н   | 1.65      | 2.16   | 0.065     | 0.085 |  |

| J   | 0.20      | 0.38   | 0.008     | 0.015 |  |

| K   | 2.92      | 3.43   | 0.115     | 0.135 |  |

| L   | 15.24 BSC |        | 0.600 BSC |       |  |

| M   | 0 °       | 15°    | 0 °       | 15°   |  |

| N   | 0.51      | 1.02   | 0.020     | 0.040 |  |

Lansdale Semiconductor reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Lansdale does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. "Typical" parameters which may be provided in Lansdale data sheets and/or specifications can vary in different applications, and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by the customer's technical experts. Lansdale Semiconductor is a registered trademark of Lansdale Semiconductor, Inc.