# SL8270, SL8271

## Legacy Device: Signetics S8270, S8271

#### DESCRIPTION

The 8270 is a 4-bit Shift Register with both serial and parallel data entry capability.

The data input lines are single-ended true input data lines which condition their specific register bit location after an enabled clocking transition. Since data transfer is synchronous with clock, data may be transferred in any serial/parallel input/output relationship.

The internal design uses level sensitive binaries which respond to the negative-going clock transition. A buffer clock driver has been included to minimize input clock loading. Mode control logic is available to determine three possible control states. These register states are serial shift right mode, parallel enter mode, and no change or hold mode. These states accomplish logical decoding for system control. The truth table for the control modes is shown below.

For applications not requiring the hold mode, the load input may be tied high and the shift input used as the mode control.

The 8271 provides a direct reset (R<sub>D</sub>), and a  $\overline{D_{out}}$  line in addition to the available outputs of the 8270 element. The fan-out specification for this output is the same as the true outputs of the 8270 element.

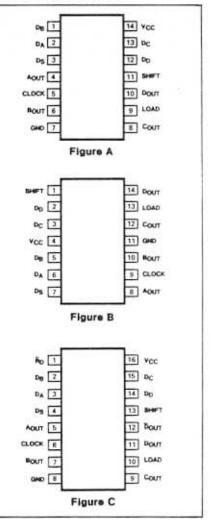

ORDERING CODE (See Section 9 for further Package and Ordering Information)

| PACKAGES    | PIN<br>CONF.   | COMMERCIAL RANGES |   |                    | MILITARY RANGES  |

|-------------|----------------|-------------------|---|--------------------|------------------|

| Plastic DIP | Fig.A<br>Fig.C | N8270N<br>N8271N  | : | N82S70N<br>N82S71N |                  |

| Ceramic DIP | Fig.A<br>Fig.C | N8270F<br>N8271F  | : | N82S70F<br>N82S71F | S8270F<br>S8271F |

| Flatpak     | Fig.B<br>Fig.A |                   |   |                    | S8270W<br>S8271W |

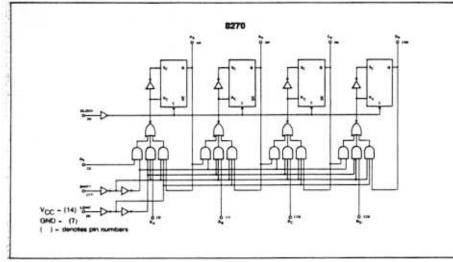

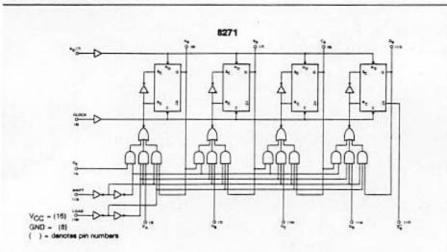

#### LOGIC DIAGRAM

#### **PIN CONFIGURATIONS**

#### MODE SELECT-FUNCTION TABLE

| CONTROL STATE  | LOAD | SHIFT |

|----------------|------|-------|

| Hold           | L    | L     |

| Parallel Entry | н    | L     |

| Shift Right    | L    | н     |

| Shift Right    | н    | н     |

H = HIGH voltage level

L = LOW voltage level

## LOGIC DIAGRAM

#### DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE<sup>(b)</sup>

| PARAMETER |                                       | TEST CONDITIONS                                                   | 8270 |      | 8271 |          | UNIT     |

|-----------|---------------------------------------|-------------------------------------------------------------------|------|------|------|----------|----------|

|           |                                       |                                                                   | Min  | Max  | Min  | Max      | - Unit   |

| VOH       | Output HIGH voltage                   | V <sub>CC</sub> = 4.75V, I <sub>OH</sub> = -800µA                 | 2.6  |      | 2.6  |          | v        |

| VOL       | Output LOW voltage                    | V <sub>CC</sub> = 4.75V, i <sub>OL</sub> = 11.2mA                 |      | 0.4  |      | 0.4      | v        |

| ΙH        | Input HIGH current<br>Reset 8271 only | V <sub>CC</sub> = 5.25V, V <sub>IN</sub> = 4.5V                   |      | 40   |      | 40<br>40 | μА<br>μА |

| ۱         | Input LOW current                     | V <sub>CC</sub> = 5.25V, V <sub>IN</sub> = 0.4V                   |      | -1.2 |      | -1.2     | mA       |

| VBD       | Voltage breakdown                     | <ul> <li>V<sub>CC</sub> = 5.25V, I<sub>IN</sub> = 10mA</li> </ul> | 5.5  |      |      |          | v        |

| lcc       | Supply current                        | V <sub>CC</sub> = 5.25V                                           |      | 47   |      | 65       | mA       |

### DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE(b)

| PARAMETER |                                                                          | TEST CONDITIONS                                  | 82\$70 |              | 82571 |              | UNIT     |

|-----------|--------------------------------------------------------------------------|--------------------------------------------------|--------|--------------|-------|--------------|----------|

|           |                                                                          |                                                  | Min    | Max          | Min   | Max          | UNIT     |

| VOH       | Output HIGH voltage                                                      | V <sub>CC</sub> = 4.75V, I <sub>OH</sub> = 1.0mA | 2.7    |              | 2.7   |              | v        |

| VOL       | Output LOW voltage                                                       | V <sub>CC</sub> = 4.75V, I <sub>OL</sub> = 20mA  |        | 0.5          |       | 0.5          | ٧        |

| ін        | Input HIGH current<br>Reset 82S71 only                                   | V <sub>CC</sub> = 5.25V                          | -      | 10           |       | 10<br>10     | μΑ<br>μΑ |

| μ         | Input LOW current<br>Load, Data, Clock inputs<br>Shift,Reset(82S7 1only) | V <sub>CC</sub> = 5.25V, V <sub>IN</sub> = 0.5V  |        | -400<br>-800 |       | -400<br>-800 | μА<br>μА |

| VBD       | Voltage breakdown                                                        | $V_{CC} = 4.75V$ , $I_{IN} = tmA$                | 5.5    |              | 5.5   |              | v        |

| VCD       | Input clamp voltage                                                      | $V_{CC} = 4.75, I_{IN} = -18mA$                  |        | -1.2         |       | -1.2         | v        |

| lcc       | Supply current                                                           | V <sub>CC</sub> = 5.25V                          |        | 90           |       | 90           | mA       |

Vote

For family dc characteristics, see inside front cover for 54/74 and 54H/74H, and see inside back cover for 54S/74S and 54LS/74LS specifications.

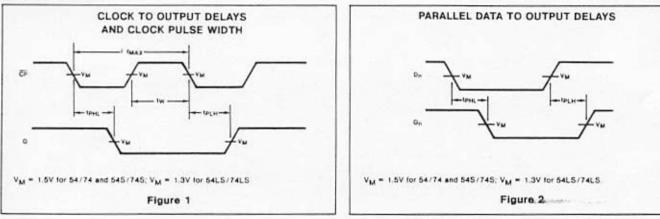

# AC CHARACTERISTICS: TA = 25° C (See Section 4 for Waveforms and Conditions)

|                  |                                                                                                                  |                 | 8270/71                                                                                                                     |          | 82570/571                                      |          |          |

|------------------|------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------|----------|----------|

| PARAMETER        |                                                                                                                  | TEST CONDITIONS | $\begin{array}{l} \mathbf{C_L} = \mathbf{21pF} \\ \mathbf{R_1} = \mathbf{co}\Omega \\ \mathbf{R_2} = 127\Omega \end{array}$ |          | C <sub>L</sub> = 15pF<br>R <sub>L</sub> = 280Ω |          |          |

| _                | and the second |                 | Min                                                                                                                         | Max      | Min                                            | Max      | 1        |

| <sup>f</sup> MAX | Maximum clock frequency                                                                                          | Figure 1        | 15                                                                                                                          |          | 40                                             |          | MHz      |

| tPLH<br>tPHL     | Propagation delay<br>Clock to output                                                                             | Figure 1        |                                                                                                                             | 40<br>40 |                                                | 20<br>20 | ns<br>ns |

| tPLH<br>tPHL     | Propagation delay<br>Reset to output                                                                             | Figure 2        |                                                                                                                             | 40<br>40 |                                                | 16<br>16 | ns<br>ns |

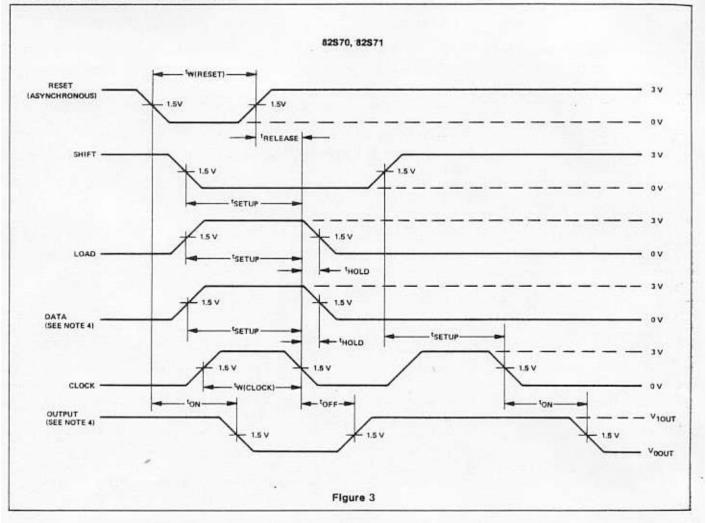

# AC SET-UP REQUIREMENTS: TA = 25° C (See Section 4 for Waveforms and Conditions)

|                | PARAMETER                             | TEST CONDITIONS | 827 | 0/71 | 8257 | 82570/571 |      |

|----------------|---------------------------------------|-----------------|-----|------|------|-----------|------|

|                |                                       |                 | Min | Max  | Min  | Max       | UNIT |

| tw             | Clock pulse width                     | Figure 1        | 20  |      | 8.0  |           | ns   |

| tw             | Reset pulse width                     | Figure 2        | 30  |      | 9.0  |           | ns   |

| ts             | Set-up time<br>Data to clock          | Figure 3        | 30  |      | 3.0  |           | ns   |

| th             | Hold time<br>Data to clock            | Figure 3        | D   |      | 2.0  |           | ns   |

| t <sub>8</sub> | Set-up time Load<br>or Shift to clock | Figure 3        | 15  |      | 6.0  |           | ns   |

| ۱'n            | Hold time Load<br>or Shift to clock   | Figure 3        | o   |      | o    |           | ns   |

| trec           | Recovery time<br>MR to clock          | Figure 3        | 30  |      | 10   |           | ns   |

|                |                                       |                 |     |      |      | 1.5       |      |

#### AC WAVEFORMS

#### AC TEST FIGURE AND WAVEFORMS

Lansdale Semiconductor reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Lansdale does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. "Typical" parameters which may be provided in Lansdale data sheets and/or specifications can vary in different applications, and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by the customer's technical experts. Lansdale Semiconductor is a registered trademark of Lansdale Semiconductor, Inc.