ML145026 ML145027 ML145028 Encoder and Decoder Pairs

# CMOS

# Legacy Device: Motorola/Freescale MC145026, MC145027, MC145028

These devices are designed to be used as encoder/decoder pairs in remote control applications.

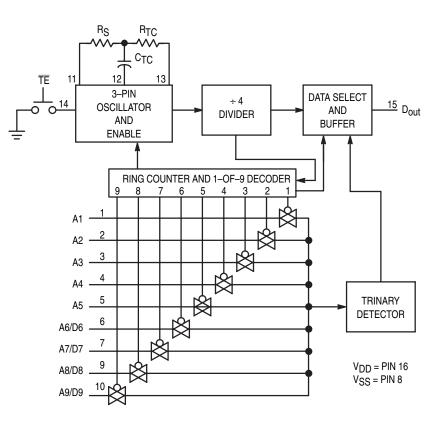

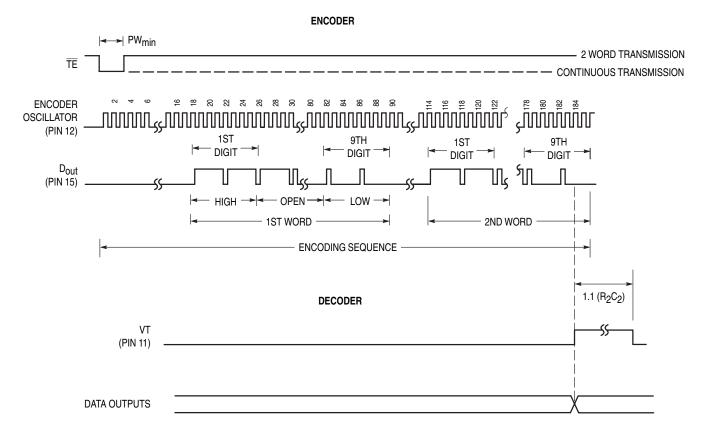

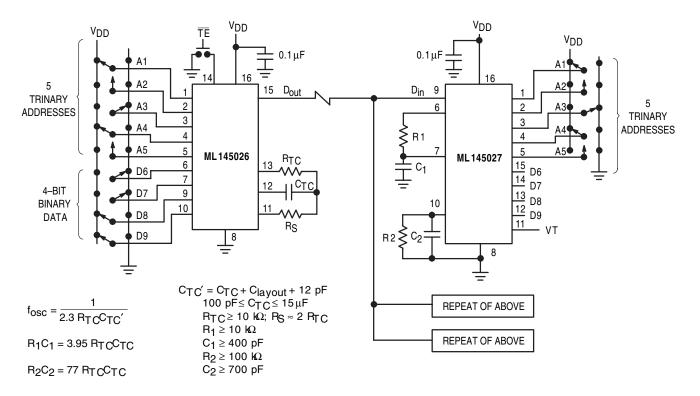

The ML145026 encodes nine lines of information and serially sends this information upon receipt of a transmit enable ( $\overline{\text{TE}}$ ) signal. The nine lines may be encoded with trinary data (low, high, or open) or binary data (low or high). The words are transmitted twice per encoding sequence to increase security.

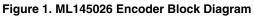

The ML145027 decoder receives the serial stream and interprets five of the trinary digits as an address code. Thus, 243 addresses are possible. If binary data is used at the encoder, 32 addresses are possible. The remaining serial information is interpreted as four bits of binary data. The valid transmission (VT) output goes high on the ML145027 when two conditions are met. First, two addresses must be consecutively received (in one encoding sequence) which both match the local address. Second, the 4 bits of data must match the last valid data received. The active VT indicates that the information at the Data output pins has been updated.

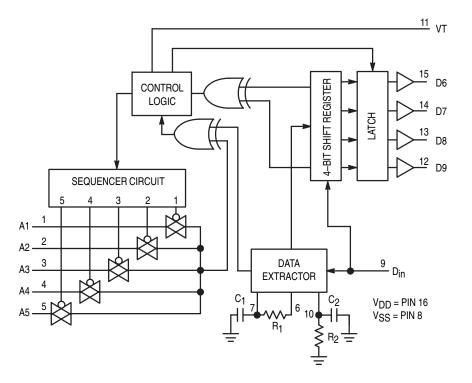

The ML145028 decoder treats all nine trinary digits as an address which allows 19,683 codes. If binary data is encoded, 512 codes are possible. The VT output goes high on the ML145028 when two addresses are consecutively received (in one encoding sequence) which both match the local address.

- Operating Temperature Range:  $T_A = -40$  to  $+85^{\circ}C$

- Very–Low Standby Current for the Encoder: 300 nA Maximum @ 25°C

- · Interfaces with RF, Ultrasonic, or Infrared Modulators and Demodulators

- RC Oscillator, No Crystal Required

- High External Component Tolerance; Can Use  $\pm$  5% Components

- Internal Power–On Reset Forces All Decoder Outputs Low

- Operating Voltage Range: ML145026 = 2.5 to 18 V\*

- ML145027, ML145028 = 4.5 to 18 V

- For Infrared Applications, See Application Note AN1016/D

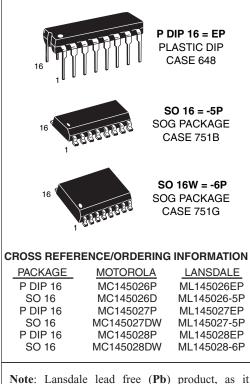

PIN ASSIGNMENTS

|                   | ML1450<br>ENCOD |    |                    |                   | ML1450<br>DECODE |    | i                                |                   |    | 45028<br>ODERS | 6                              |

|-------------------|-----------------|----|--------------------|-------------------|------------------|----|----------------------------------|-------------------|----|----------------|--------------------------------|

| A1 [              | 1•              | 16 | D v <sub>DD</sub>  | A1 [              | 1•               | 16 | D V <sub>DD</sub>                | A1 [              | 1● | 16             | D v <sub>DD</sub>              |

| A2 [              | 2               | 15 | ] D <sub>out</sub> | A2 [              | 2                | 15 | D6                               | A2 [              | 2  | 15             | D A6                           |

| АЗ [              | 3               | 14 | ) TE               | аз [              | 3                | 14 | D7                               | АЗ [              | 3  | 14             | D A7                           |

| A4 [              | 4               | 13 | ] R <sub>TC</sub>  | A4 [              | 4                | 13 | ] D8                             | A4 [              | 4  | 13             | ] A8                           |

| A5 [              | 5               | 12 | ] с <sub>тс</sub>  | A5 [              | 5                | 12 | D9                               | A5 [              | 5  | 12             | ] A9                           |

| A6/D6 [           | 6               | 11 | ] R <sub>S</sub>   | R <sub>1</sub> [  | 6                | 11 | ] VT                             | R <sub>1</sub> [  | 6  | 11             | ] VT                           |

| A7/D7 [           | 7               | 10 | ] A9/D9            | с <sub>1</sub> [  | 7                | 10 | ] R <sub>2</sub> /C <sub>2</sub> | C <sub>1</sub> [  | 7  | 10             | R <sub>2</sub> /C <sub>2</sub> |

| v <sub>ss</sub> [ | 8               | 9  | A8/D8              | v <sub>ss</sub> C | 8                | 9  | ] D <sub>in</sub>                | v <sub>ss</sub> [ | 8  | 9              | D D <sub>in</sub>              |

becomes available, will be identified by a part number prefix change from ML to MLE.

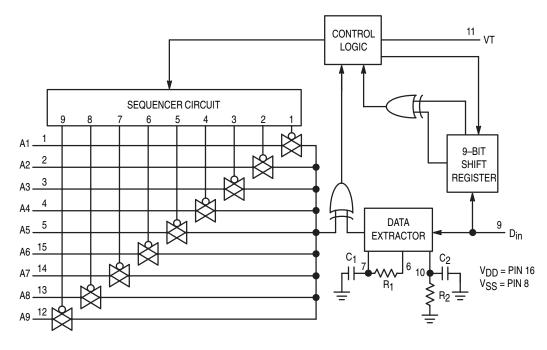

Figure 2. ML145027 Decoder Block Diagram

Figure 3. ML145028 Decoder Block Diagram

# MAXIMUM RATINGS\* (Voltages Referenced to VSS)

| Rating           | Symbol                                          | Value                          | Unit |

|------------------|-------------------------------------------------|--------------------------------|------|

| V <sub>DD</sub>  | DC Supply Voltage                               | – 0.5 to + 18                  | V    |

|                  |                                                 |                                |      |

| V <sub>in</sub>  | DC Input Voltage                                | – 0.5 to V <sub>DD</sub> + 0.5 | V    |

| Vout             | DC Output Voltage                               | – 0.5 to V <sub>DD</sub> + 0.5 | V    |

| l <sub>in</sub>  | DC Input Current, per Pin                       | ± 10                           | mA   |

| lout             | DC Output Current, per Pin                      | ± 10                           | mA   |

| PD               | Power Dissipation, per Package                  | 500                            | mW   |

| T <sub>stg</sub> | Storage Temperature                             | – 65 to + 150                  | °C   |

| ТL               | Lead Temperature, 1 mm from Case for 10 Seconds | 260                            | °C   |

\* Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the limits in the Electrical Characteristics tables or Pin Descriptions section. This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high–impedance circuit. For proper operation,  $V_{in}$  and  $V_{out}$  should be constrained to the range  $V_{SS} \leq (V_{in} \text{ or } V_{out}) \leq V_{DD}.$

|                 |                                                                                                                                              |                        | Guaranteed Limit                  |                      |                                   |                          |                                   |                      |      |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------------------|----------------------|-----------------------------------|--------------------------|-----------------------------------|----------------------|------|

|                 |                                                                                                                                              | v <sub>DD</sub>        | - 4                               | 0°C                  | 25                                | °C                       | 85                                | °C                   | Unit |

| Symbol          | Characteristic                                                                                                                               |                        | Min                               | Max                  | Min                               | Max                      | Min                               | Max                  |      |

| V <sub>OL</sub> | Low–Level Output Voltage (V <sub>in</sub> = V <sub>DD</sub> or 0)                                                                            | 5.0<br>10<br>15        |                                   | 0.05<br>0.05<br>0.05 |                                   | 0.05<br>0.05<br>0.05     |                                   | 0.05<br>0.05<br>0.05 | V    |

| VOH             | High–Level Output Voltage (V <sub>in</sub> = 0 or V <sub>DD</sub> )                                                                          | 5.0<br>10<br>15        | 4.95<br>9.95<br>14.95             |                      | 4.95<br>9.95<br>14.95             | _<br>_<br>_              | 4.95<br>9.95<br>14.95             | _<br>_<br>_          | V    |

| VIL             | Low–Level Input Voltage<br>(V <sub>out</sub> = 4.5 or 0.5 V)<br>(V <sub>out</sub> = 9.0 or 1.0 V)<br>(V <sub>out</sub> = 13.5 or 1.5 V)      | 5.0<br>10<br>15        |                                   | 1.5<br>3.0<br>4.0    |                                   | 1.5<br>3.0<br>4.0        |                                   | 1.5<br>3.0<br>4.0    | V    |

| VIH             | High–Level Input Voltage<br>(V <sub>out</sub> = 0.5 or 4.5 V)<br>(V <sub>out</sub> = 1.0 or 9.0 V)<br>(V <sub>out</sub> = 1.5 or 13.5 V)     | 5.0<br>10<br>15        | 3.5<br>7.0<br>11                  |                      | 3.5<br>7.0<br>11                  |                          | 3.5<br>7.0<br>11                  |                      | V    |

| lон             | High–Level Output Current $ \begin{array}{c} (V_{Out}=2.5 \ V) \\ (V_{Out}=4.6 \ V) \\ (V_{out}=9.5 \ V) \\ (V_{out}=13.5 \ V) \end{array} $ | 5.0<br>5.0<br>10<br>15 | - 2.5<br>- 0.52<br>- 1.3<br>- 3.6 | <br><br>             | - 2.1<br>- 0.44<br>- 1.1<br>- 3.0 | <br>                     | - 1.7<br>- 0.36<br>- 0.9<br>- 2.4 | <br><br>             | mA   |

| I <sub>OL</sub> | Low–Level Output Current                                                                                                                     | 5.0<br>10<br>15        | 0.52<br>1.3<br>3.6                |                      | 0.44<br>1.1<br>3.0                |                          | 0.36<br>0.9<br>2.4                |                      | mA   |

| lin             | Input Current — TE<br>(ML145026, Pull–Up Device)                                                                                             | 5.0<br>10<br>15        | _<br>_<br>_                       |                      | 3.0<br>16<br>35                   | 11<br>60<br>120          | _<br>_<br>_                       | _<br>_<br>_          | μA   |

| l <sub>in</sub> | Input Current<br>R <sub>S</sub> (ML145026), D <sub>in</sub> (ML145027, ML145028)                                                             | 15                     | —                                 | ± 0.3                | —                                 | ± 0.3                    | —                                 | ± 1.0                | μA   |

| l <sub>in</sub> | Input Current<br>A1 – A5, A6/D6 – A9/D9 (ML145026),<br>A1 – A5 (ML145027),<br>A1 – A9 (ML145028)                                             | 5.0<br>10<br>15        |                                   |                      |                                   | ± 110<br>± 500<br>± 1000 |                                   |                      | μA   |

| C <sub>in</sub> | Input Capacitance (V <sub>in</sub> = 0)                                                                                                      | _                      | —                                 | _                    | —                                 | 7.5                      | —                                 | _                    | pF   |

| IDD             | Quiescent Current — ML145026                                                                                                                 | 5.0<br>10<br>15        |                                   |                      |                                   | 0.1<br>0.2<br>0.3        |                                   | _<br>_<br>_          | μA   |

| IDD             | Quiescent Current — ML145027, ML145028                                                                                                       | 5.0<br>10<br>15        | <br><br>                          |                      | <br><br>                          | 50<br>100<br>150         | <br><br>                          | <br><br>             | μA   |

| ldd             | Dynamic Supply Current — ML145026<br>(f <sub>C</sub> = 20 kHz)                                                                               | 5.0<br>10<br>15        |                                   |                      |                                   | 200<br>400<br>600        | _<br>_<br>_                       | _<br>_<br>_          | μA   |

| ldd             | Dynamic Supply Current — ML145027, ML145028<br>(f <sub>C</sub> = 20 kHz)                                                                     | 5.0<br>10<br>15        |                                   |                      |                                   | 400<br>800<br>1200       |                                   |                      | μA   |

# ELECTRICAL CHARACTERISTICS - ML145026\*, ML145027, and ML145028 (Voltage Referenced to V<sub>SS</sub>)

\* Also see next Electrical Characteristics table for 2.5 V specifications.

|                 |                                                                       | Guaranteed Limit |      |      |      |      |      |      |      |

|-----------------|-----------------------------------------------------------------------|------------------|------|------|------|------|------|------|------|

|                 |                                                                       | v <sub>DD</sub>  | - 4  | 0°C  | 25   | °C   | 85   | °C   |      |

| Symbol          | Characteristic                                                        |                  | Min  | Max  | Min  | Max  | Min  | Max  | Unit |

| VOL             | Low–Level Output Voltage (V <sub>in</sub> = 0 V or V <sub>DD</sub> )  | 2.5              | _    | 0.05 | —    | 0.05 | —    | 0.05 | V    |

| VOH             | High–Level Output Voltage (V <sub>in</sub> = 0 V or V <sub>DD</sub> ) | 2.5              | 2.45 | _    | 2.45 | —    | 2.45 | _    | V    |

| VIL             | Low–Level Input Voltage (V <sub>out</sub> = 0.5 V or 2.0 V)           | 2.5              | —    | 0.3  | —    | 0.3  | —    | 0.3  | V    |

| VIH             | High–Level Input Voltage (V <sub>out</sub> = 0.5 V or 2.0 V)          | 2.5              | 2.2  | —    | 2.2  | —    | 2.2  | —    | V    |

| ЮН              | High–Level Output Current (V <sub>out</sub> = 1.25 V)                 | 2.5              | 0.28 | —    | 0.25 | —    | 0.2  | —    | mA   |

| lol             | Low–Level Output Current (V <sub>out</sub> = 0.4 V)                   | 2.5              | 0.22 | —    | 0.2  | —    | 0.16 | —    | mA   |

| l <sub>in</sub> | Input Current (TE — Pull–Up Device)                                   | 2.5              | —    | —    | 0.09 | 1.8  | —    | —    | μΑ   |

| l <sub>in</sub> | Input Current (A1–A5, A6/D6–A9/D9)                                    | 2.5              | —    | —    | _    | ± 25 | _    | —    | μΑ   |

| IDD             | Quiescent Current                                                     | 2.5              | _    | _    | —    | 0.05 | —    | _    | μΑ   |

| I <sub>dd</sub> | Dynamic Supply Current (f <sub>C</sub> = 20 kHz)                      | 2.5              | _    | —    | —    | 40   | —    | _    | μΑ   |

# $\textbf{ELECTRICAL CHARACTERISTICS} - \textbf{ML145026} \hspace{0.1 cm} (\text{Voltage Referenced to V}_{SS})$

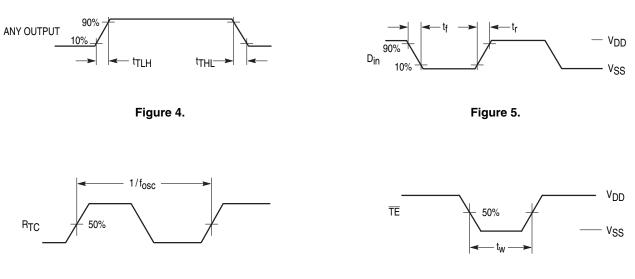

# SWITCHING CHARACTERISTICS — ML145026\*, ML145027, and ML145028 $(C_L = 50 \text{ pF}, T_A = 25^{\circ}C)$

|                                     |                                                 | Figure |                 | Guarante                | ed Limit          |      |

|-------------------------------------|-------------------------------------------------|--------|-----------------|-------------------------|-------------------|------|

| Symbol                              | Characteristic                                  | No.    | V <sub>DD</sub> | Min                     | Max               | Unit |

| <sup>t</sup> TLH <sup>, t</sup> THL | Output Transition Time                          | 4,8    | 5.0<br>10<br>15 |                         | 200<br>100<br>80  | ns   |

| tr                                  | D <sub>in</sub> Rise Time — Decoders            | 5      | 5.0<br>10<br>15 |                         | 15<br>15<br>15    | μs   |

| t <sub>f</sub>                      | D <sub>in</sub> Fall Time — Decoders            | 5      | 5.0<br>10<br>15 |                         | 15<br>5.0<br>4.0  | μs   |

| f <sub>osc</sub>                    | Encoder Clock Frequency                         | 6      | 5.0<br>10<br>15 | 0.001<br>0.001<br>0.001 | 2.0<br>5.0<br>10  | MHz  |

| f                                   | Decoder Frequency — Referenced to Encoder Clock | 12     | 5.0<br>10<br>15 | 1.0<br>1.0<br>1.0       | 240<br>410<br>450 | kHz  |

| t <sub>w</sub>                      | TE Pulse Width — Encoders                       | 7      | 5.0<br>10<br>15 | 65<br>30<br>20          |                   | ns   |

\* Also see next Switching Characteristics table for 2.5 V specifications.

# SWITCHING CHARACTERISTICS — ML145026 ( $C_L = 50 \text{ pF}, T_A = 25^{\circ}C$ )

|                |                         | Figure |                 | Guarante | ed Limit |      |

|----------------|-------------------------|--------|-----------------|----------|----------|------|

| Symbol         | Characteristic          | No.    | V <sub>DD</sub> | Min      | Max      | Unit |

| tTLH, tTHL     | Output Transition Time  | 4, 8   | 2.5             | _        | 450      | ns   |

| fosc           | Encoder Clock Frequency | 6      | 2.5             | 1.0      | 250      | kHz  |

| t <sub>w</sub> | TE Pulse Width          | 7      | 2.5             | 1.5      | _        | μs   |

\* Includes all probe and fixture capacitance.

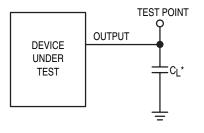

Figure 8. Test Circuit

### **OPERATING CHARACTERISTICS**

#### ML145026

The encoder serially transmits trinary data as defined by the state of the A1 – A5 and A6/D6 – A9/D9 input pins. These pins may be in either of three states (low, high, or open) allowing 19,683 possible codes. The transmit sequence is initiated by a low level on the  $\overline{\text{TE}}$  input pin. Upon power–up, the ML145026 can continuously transmit as long as  $\overline{\text{TE}}$  remains low (also, the device can transmit two–word sequences by pulsing  $\overline{\text{TE}}$  low). However, no ML145026 application should be designed to rely upon the first data word transmitted immediately after power–up because this word may be invalid. Between the two data words, no signal is sent for three data periods (see Figure 10).

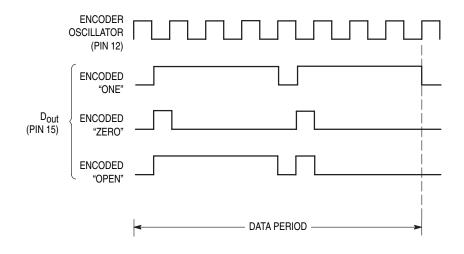

Each transmitted trinary digit is encoded into pulses (see Figure 11). A logic 0 (low) is encoded as two consecutive short pulses, a logic 1 (high) as two consecutive long pulses, and an open (high impedance) as a long pulse followed by a short pulse. The input state is determined by using a weak"output" device to try to force each input high then low. If only a high state results from the two tests, the input is assumed to be hard wired to V<sub>DD</sub>. If only a low state is obtained, the input is assumed to be hardwired to V<sub>SS</sub>. If both a high and a low can be forced at an input, an open is assumed and is encoded as such. The "high" and "low" levels are 70% and 30% of the supply voltage as shown in the Electrical Characteristics table. The weak "output" device sinks/sources up to 110  $\mu$ A at a 5 V supply level, 500  $\mu$ A at 10 V, and 1 mA at 15 V.

The  $\overline{\text{TE}}$  input has an internal pull–up device so that a simple switch may be used to force the input low. While  $\overline{\text{TE}}$  is high and the second–word transmission has timed out, the encoder is completely disabled, the oscillator is inhibited, and the current drain is reduced to quiescent current. When  $\overline{\text{TE}}$  is brought low, the oscillator is started and the transmit sequence begins. The inputs are then sequentially selected, and determinations are made as to the input logic states. This information is serially transmitted via the D<sub>out</sub> pin.

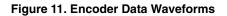

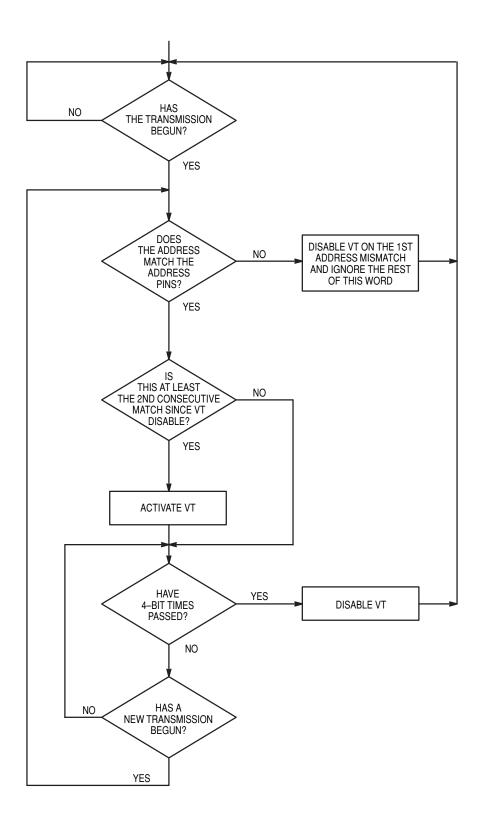

## ML145027

This decoder receives the serial data from the encoder and outputs the data, if it is valid. The transmitted data, consisting of two identical words, is examined bit by bit during reception. The first five trinary digits are assumed to be the address. If the received address matches the local address, the next four (data) bits are internally stored, but are not transferred to the output data latch. As the second encoded word is received, the address must again match. If a match occurs, the new data bits are checked against the previously stored data bits. If the two nibbles of data (four bits each) match, the data is transferred to the output data latch by VT and remains until new data replaces it. At the same time, the VT output pin is brought high and remains high until an error is received or until no input signal is received for four data periods (see Figure 10).

Although the address information may be encoded in trinary, the data information must be either a 1 or 0. A trinary (open) data line is decoded as a logic 1.

#### ML145028

This decoder operates in the same manner as the ML145027 except that nine address lines are used and no data output is available. The VT output is used to indicate that a valid address has been received. For transmission security, two identical transmitted words must be consecutively received before a VT output signal is issued.

The ML145028 allows 19,683 addresses when trinary levels are used. 512 addresses are possible when binary levels are used.

#### **PIN DESCRIPTIONS**

#### ML145026 ENCODER

#### A1 – A5, A6/D6 – A9/D9 Address, Address/Data Inputs (Pins 1 – 7, 9, and 10)

These address/data inputs are encoded and the data is sent serially from the encoder via the D<sub>out</sub> pin.

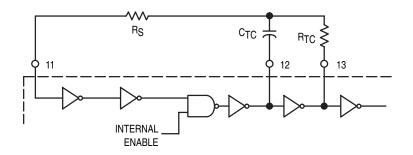

#### **RS, CTC, RTC** (Pins 11, 12, and 13)

These pins are part of the oscillator section of the encoder (see Figure 9).

If an external signal source is used instead of the internal oscillator, it should be connected to the RS input and the RTC and CTC pins should be left open.

#### TE

#### Transmit Enable (Pin 14)

This active-low transmit enable input initiates transmission when forced low. An internal pull-up device keeps this input normally high. The pull-up current is specified in the Electrical Characteristics table.

## Dout

#### Data Out (Pin 15)

This is the output of the encoder that serially presents the encoded data word.

## VSS

#### Negative Power Supply (Pin 8)

The most–negative supply potential. This pin is usually ground.

## VDD

## Positive Power Supply (Pin 16).

The most-positive power supply pin.

## ML145027 AND ML145028 DECODERS

#### A1 – A5, A1 – A9 Address Inputs (Pins 1 – 5)—ML145027, Address Inputs (Pins 1 – 5, 15, 14, 13, 12)—ML145028

These are the local address inputs. The states of these pins must match the appropriate encoder inputs for the VT pin to go high. The local address may be encoded with trinary or binary data.

## D6 – D9

## Data Outputs (Pins 15, 14, 13, 12)-ML145027 Only

These outputs present the binary information that is on encoder inputs A6/D6 through A9/D9. Only binary data is

acknowledged; a trinary open at the ML145026 encoder is decoded as a high level (logic 1).

# Din

# Data In (Pin 9)

This pin is the serial data input to the decoder. The input voltage must be at CMOS logic levels. The signal source driving this pin must be DC coupled.

# R<sub>1</sub>, C<sub>1</sub>

## Resistor 1, Capacitor 1 (Pins 6, 7)

As shown in Figures 2 and 3, these pins accept a resistor and capacitor that are used to determine whether a narrow pulse or wide pulse has been received. The time constant  $R_1 \ge C_1$  should be set to 1.72 encoder clock periods:

$R_1 C_1 = 3.95 R_{TC} C_{TC}$

# $R_2/C_2$

# **Resistor 2/Capacitor 2 (Pin 10)**

As shown in Figures 2 and 3, this pin accepts a resistor and capacitor that are used to detect both the end of a received word and the end of a transmission. The time constant  $R_2 \ge C_2$  should be 33.5 encoder clock periods (four data periods per Figure 11):  $R_2 C_2 = 77 R_{TC} C_{TC}$ . This time constant is used to determine whether the D<sub>in</sub> pin has remained low for four data periods (end of transmission). A separate on-chip com-

parator looks at the voltage–equivalent two data periods (0.4  $R_2 C_2$ ) to detect the dead time between received words within a transmission.

## VT

## Valid Transmission Output (Pin 11)

This valid transmission output goes high after the second word of an encoding sequence when the following conditions are satisfied:

- 1. the received addresses of both words match the local de-coder address, and

- 2. the received data bits of both words match.

VT remains high until either a mismatch is received or no input signal is received for four data periods.

## VSS

## Negative Power Supply (Pin 8)

The most–negative supply potential. This pin is usually ground.

#### VDD

# **Positive Power Supply (Pin 16)**

The most-positive power supply pin.

This oscillator operates at a frequency determined by the external RC network; i.e.,

$$f \approx \frac{1}{2.3 \text{ R}_{\text{TC}} \text{ C}_{\text{TC}}'}$$

(Hz)

for 1 kHz

$$\leq$$

f  $\leq$  400 kHz

where:  $CTC' = CTC + C_{layout} + 12 \text{ pF}$   $R_S \approx 2 \text{ R}_{TC}$   $R_S \ge 20 \text{ k}$   $R_{TC} \ge 10 \text{ k}$  $400 \text{ pF} < C_{TC} < 15 \mu\text{F}$  The value for R<sub>S</sub> should be chosen to be  $\ge 2$  times R<sub>TC</sub>. This range ensures that current through R<sub>S</sub> is insignificant compared to current through R<sub>TC</sub>. The upper limit for R<sub>S</sub> must ensure that R<sub>S</sub> x 5 pF (input capacitance) is small compared to R<sub>TC</sub> x C<sub>TC</sub>.

For frequencies outside the indicated range, the formula is less accurate. The minimum recommended oscillation frequency of this circuit is 1 kHz. Susceptibility to externally induced noise signals may occur for frequencies below 1 kHz and/or when resistors utilized are greater than 1 M $\Omega$ .

#### Figure 9. Encoder Oscillator Information

Figure 12. f<sub>max</sub> vs C<sub>layout</sub> — Decoders Only

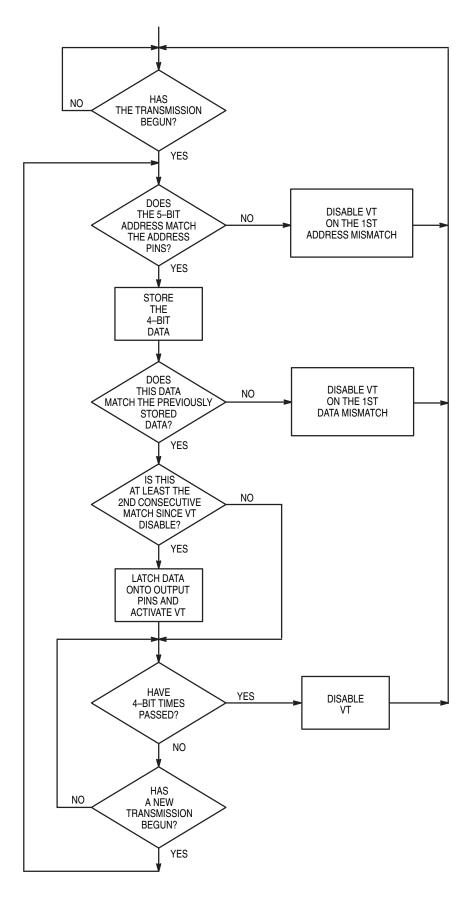

Figure 13. ML145027 Flowchart

Figure 14. ML145028 Flowchart

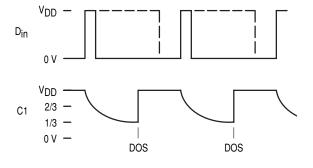

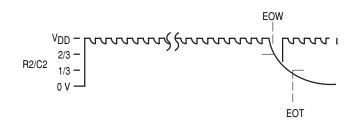

#### ML145027 AND ML145028 TIMING

To verify the ML145027 or ML145028 timing, check thewaveforms on  $C_1$  (Pin 7) and  $R_2/C_2$  (Pin 10) as compared to the incoming data waveform on  $D_{in}$  (Pin 9).

The R–C decay seen on C1 discharges down to 1/3 VDD before being reset to VDD. This point of reset (labelled "DOS" in Figure 15) is the point in time where the decision is made whether the data seen on D<sub>in</sub> is a 1 or 0. DOS should not be too close to the D<sub>in</sub> data edges or intermittent operation may occur.

The other timing to be checked on the ML145027 and ML145028 is on  $R_2/C_2$  (see Figure 16). The R–C decay is continually reset to  $V_{DD}$  as data is being transmitted. Only between words and after the end–of–transmission (EOT) does  $R_2/C_2$  decay significantly from  $V_{DD}$ .  $R_2/C_2$  can be used to identify the internal end–of–word (EOW) timing edge which is generated when  $R_2/C_2$  decays to 2/3  $V_{DD}$ . The internal EOT timing edge occurs when  $R_2/C_2$  decays to 1/3  $V_{DD}$ . When the waveform is being observed, the R–C decay should go down between the 2/3 and 1/3  $V_{DD}$  levels, but not too close to either level before data transmission on  $D_{in}$  resumes.

Verification of the timing described above should ensure a good match between the ML145026 transmitter and the ML145027 and ML145028 receivers.

Figure 15. R-C Decay on Pin 7 (C1)

Figure 16. R-C Decay on Pin 10 (R2/C2)

| (CTC' = CTC)           | ; + 20 pF | )       |       |                |                |                |                |

|------------------------|-----------|---------|-------|----------------|----------------|----------------|----------------|

| f <sub>osc</sub> (kHz) | ₽tc       | Стс     | RS    | R <sub>1</sub> | С <sub>1</sub> | R <sub>2</sub> | C <sub>2</sub> |

| 362                    | 10 k      | 120 pF  | 20 k  | 10 k           | 470 pF         | 100 k          | 910 pF         |

| 181                    | 10 k      | 240 pF  | 20 k  | 10 k           | 910 pF         | 100 k          | 1800 pF        |

| 88.7                   | 10 k      | 490 pF  | 20 k  | 10 k           | 2000 pF        | 100 k          | 3900 pF        |

| 42.6                   | 10 k      | 1020 pF | 20 k  | 10 k           | 3900 pF        | 100 k          | 7500 pF        |

| 21.5                   | 10 k      | 2020 pF | 20 k  | 10 k           | 8200 pF        | 100 k          | 0.015µF        |

| 8.53                   | 10 k      | 5100 pF | 20 k  | 10 k           | 0.02µF         | 200 k          | 0.02µF         |

| 1.71                   | 50 k      | 5100 pF | 100 k | 50 k           | 0.02µF         | 200 k          | 0.1µF          |

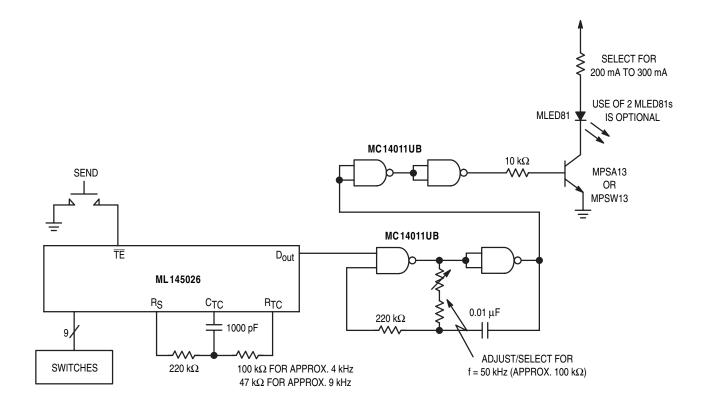

Figure 17. Typical Application

## Legacy Applications Information

### **INFRARED TRANSMITTER**

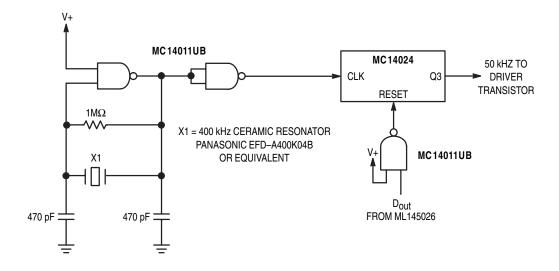

In Figure 18, the ML145026 encoder is set to run at an oscillator frequency of about 4 to 9 kHz. Thus, the time required for a complete two–word encoding sequence is about 20 to 40 ms. The data output from the encoder gates an RC oscillator running at 50 kHz; the oscillator shown starts rapidly enough to be used in this application. When the "send" button is not depressed, both the ML145026 and oscillator are in a low–power standby state. The RC oscillator has to be trimmed for 50 kHz and has some drawbacks for frequency stability. A superior system uses a ceramic resonator oscillator running at 400 kHz. This oscillator feeds a divider as shown in Figure 19. The unused inputs of the MC14011UB must be grounded.

The MLED81 IRED is driven with the 50 kHz square wave at about 200 to 300 mA to generate the carrier. If desired, two IREDs wired in series can be used (see Application Note AN1016 for more information). The bipolar IRED switch, shown in Figure 18, offers two advantages over a FET. First, a logic FET has too much gate capacitance for the MC14011UB to drive without waveform distortion. Second, the bipolar drive permits lower supply voltages, which are an advantage in portable battery–powered applications.

The configuration shown in Figure 18 operates over a supply range of 4.5 to 18 V. A low–voltage system which operates down to 2.5 V could be realized if the oscillator section of a MC74HC4060 is used in place of the MC14011UB. The data output of the ML145026 is inverted and fed to the RESET pin of the MC74HC4060. Alternately, the MC74HCU04 could be used for the oscillator.

For information on the MC14011UB, MC74HCU04 and MC74HC4060 consult ON Semiconductor.

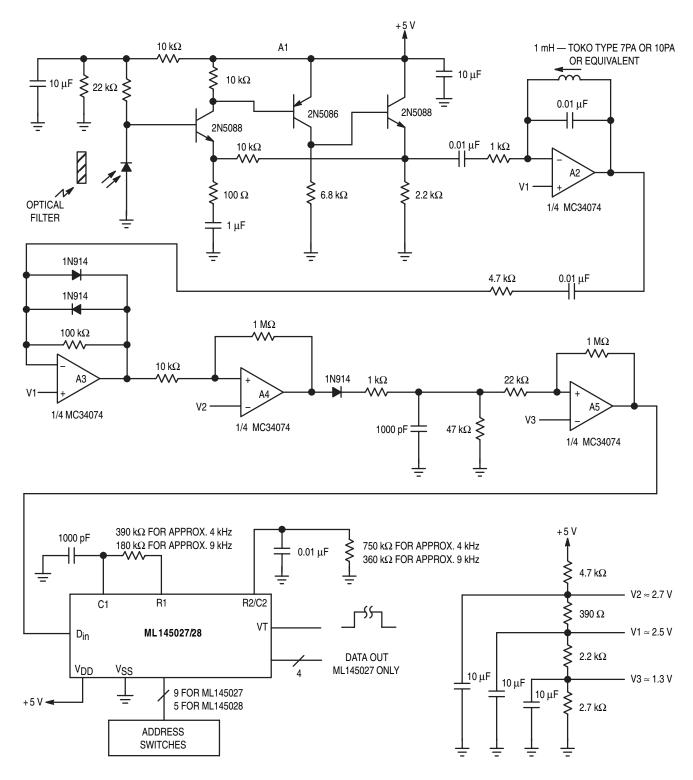

## **INFRARED RECEIVER**

The receiver in Figure 20 couples an IR–sensitive diode to input preamp A1, followed by band–pass amplifier A2 with again of about 10. Limiting stage A3 follows, with an output of about 800 mV p–p. The limited 50 kHz burst is detected by comparator A4 that passes only positive pulses, and peak–detected and filtered by a diode/RC network to extract the data envelope from the burst. Comparator A5 boosts the signal to logic

levels compatible with the ML145027/28 data input. The D<sub>in</sub> pin of these decoders is a standard CMOS high–impedance input which must not be allowed to float. Therefore, direct coupling from A5 to the decoder input is utilized.

Shielding should be used on at least A1 and A2, with good ground and high–sensitivity circuit layout techniques applied. For operation with supplies higher than + 5 V, limiter A4's positive output swing needs to be limited to 3 to 5 V. This is accomplished via adding a zener diode in the negative feedback path, thus avoiding excessive system noise. The biasing resistor stack should be adjusted such that V3 is 1.25 to 1.5 V.

This system works up to a range of about 10 meters. The gains of the system may be adjusted to suit the individual design needs. The 100  $\Omega$  resistor in the emitter of the first 2N5088 and the 1 k $\Omega$  resistor feeding A2 may be altered if different gain is required. In general, more gain does not necessarily result in increased range. This is due to noise floor limitations. The designer should increase transmitter power and/or increase receiver aperature with Fresnal lensing to greatly improve range. See Application Note AN1016 for additional information.

For information on the MC34074 contact ON Semiconductor.

#### TRINARY SWITCH MANUFACTURERS

Midland Ross–Electronic Connector Div. Greyhill Augat/Alcoswitch Aries Electronics

The above companies may not have the switches in a DIP. For more information, call them or consult eem Electronic Engineers Master Catalog or the Gold Book. **Ask for SPDT** with center OFF.

Alternative: An SPST can be placed in series between a SPDT and the Encoder or Decoder to achieve trinary action.

Lansdale cannot recommend one supplier over another and in no way suggests that this is a complete listing of trinary switch manufacturers.

Figure 18. IRED Transmitter Using RC Oscillator to Generate Carrier Frequency

Figure 19. Using a Ceramic Resonator to Generate Carrier Frequency

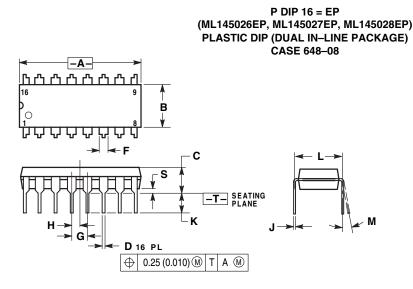

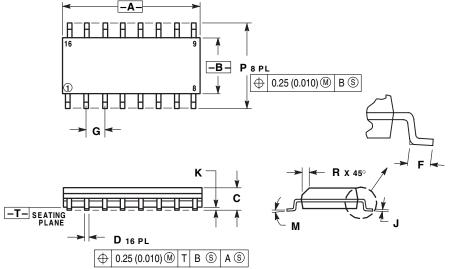

#### **OUTLINE DIMENSIONS**

| NOT | ES:    |           |          |           |           |       |

|-----|--------|-----------|----------|-----------|-----------|-------|

| 1.  | DIMEN  | SIONING   | AND TOL  | ERANCIN   | G PER AN  | ISI   |

|     | Y14.5M | l, 1982.  |          |           |           |       |

| 2.  | CONTF  | ROLLING I | DIMENSIC | DN: INCH. |           |       |

| 3.  | DIMEN  | SION L TO | CENTER   | R OF LEA  | DS WHEN   |       |

|     | FORME  | ED PARAL  | LEL.     |           |           |       |

| 4.  |        |           |          |           | E MOLD FI | LASH. |

| 5.  | ROUNE  | DED CORI  | NERS OP  | TIONAL.   |           |       |

|     |        | INC       | HES      | MILLI     | METERS    |       |

|     | DIM    | MIN       | MAX      | MIN       | MAX       |       |

|     | Α      | 0.740     | 0.770    | 18.80     | 19.55     |       |

|     | В      | 0.250     | 0.270    | 6.35      | 6.85      |       |

|     | С      | 0.145     | 0.175    | 3.69      | 4.44      |       |

|     | D      | 0.015     | 0.021    | 0.39      | 0.53      |       |

|     | F      | 0.040     | 0.70     | 1.02      | 1.77      |       |

|     | G      | 0.100     | BSC      | 2.54      | BSC       |       |

|     | н      | 0.050     | BSC      | 1.27      | BSC       |       |

|     | J      | 0.008     | 0.015    | 0.21      | 0.38      |       |

|     | K      | 0 110     | 0 1 3 0  | 2 80      | 3 30      |       |

0.305

10

SO 16 = -5P SOG (SMALL OUTLINE GULL-WING) PACKAGE (ML145026-5P) CASE 751B-05

NOTES:

0.295

S 0.020 0.040

L M

DIMENSIONING AND TOLERANCING PER ANSI 1. Y14.5M, 1982. CONTROLLING DIMENSION: MILLIMETER.

7.74

10

7.50

0

0.51 1.01

- 2.

- DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION. 3.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE. 4.

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR 5. PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLI | METERS | INCHES |       |  |

|-----|-------|--------|--------|-------|--|

| DIM | MIN   | MAX    | MIN    | MAX   |  |

| Α   | 9.80  | 10.00  | 0.386  | 0.393 |  |

| В   | 3.80  | 4.00   | 0.150  | 0.157 |  |

| С   | 1.35  | 1.75   | 0.054  | 0.068 |  |

| D   | 0.35  | 0.49   | 0.014  | 0.019 |  |

| F   | 0.40  | 1.25   | 0.016  | 0.049 |  |

| G   | 1.27  | BSC    | 0.050  | BSC   |  |

| ſ   | 0.19  | 0.25   | 0.008  | 0.009 |  |

| Κ   | 0.10  | 0.25   | 0.004  | 0.009 |  |

| М   | 0 °   | 7°     | 0 °    | 7°    |  |

| Ρ   | 5.80  | 6.20   | 0.229  | 0.244 |  |

| R   | 0.25  | 0.50   | 0.010  | 0.019 |  |

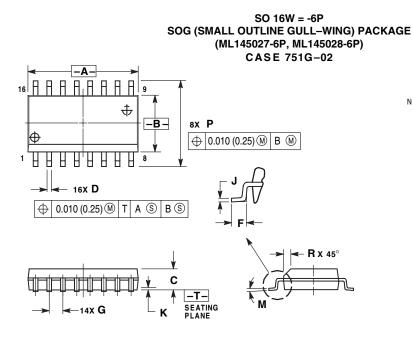

# **OUTLINE DIMENSIONS**

NOTES: 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. CONTROLLING DIMENSION: MILLIMETER.

- CONTROLLING DIMENSION: MILLIMETER. DIMENSIONS A AND B DO NOT INCLUDE MOLD 2. 3.

- PROTRUSION.

- 4. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE

| 5. | DIMENSION D DOES NOT INCLUDE DAMBAR       |

|----|-------------------------------------------|

|    | PROTRUSION. ALLOWABLE DAMBAR              |

|    | PROTRUSION SHALL BE 0.13 (0.005) TOTAL IN |

|    | EXCESS OF D DIMENSION AT MAXIMUM          |

|    | MATERIAL CONDITION.                       |

|     | MILLI | METERS | INCHES |       |  |

|-----|-------|--------|--------|-------|--|

| DIM | MIN   | MAX    | MIN    | MAX   |  |

| Α   | 10.15 | 10.45  | 0.400  | 0.411 |  |

| В   | 7.40  | 7.60   | 0.292  | 0.299 |  |

| С   | 2.35  | 2.65   | 0.093  | 0.104 |  |

| D   | 0.35  | 0.49   | 0.014  | 0.019 |  |

| F   | 0.50  | 0.90   | 0.020  | 0.035 |  |

| G   | 1.27  | BSC    | 0.050  | BSC   |  |

| J   | 0.25  | 0.32   | 0.010  | 0.012 |  |

| K   | 0.10  | 0.25   | 0.004  | 0.009 |  |

| М   | 0 °   | 7 °    | 0 °    | 7 °   |  |

| Р   | 10.05 | 10.55  | 0.395  | 0.415 |  |

| R   | 0.25  | 0.75   | 0.010  | 0.029 |  |

Lansdale Semiconductor reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Lansdale does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Typical " parameters which may be provided in Lansdale data sheets and/or specifications can vary in different applications, and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by the customer's technical experts. Lansdale Semiconductor is a registered trademark of Lansdale Semiconductor, Inc.